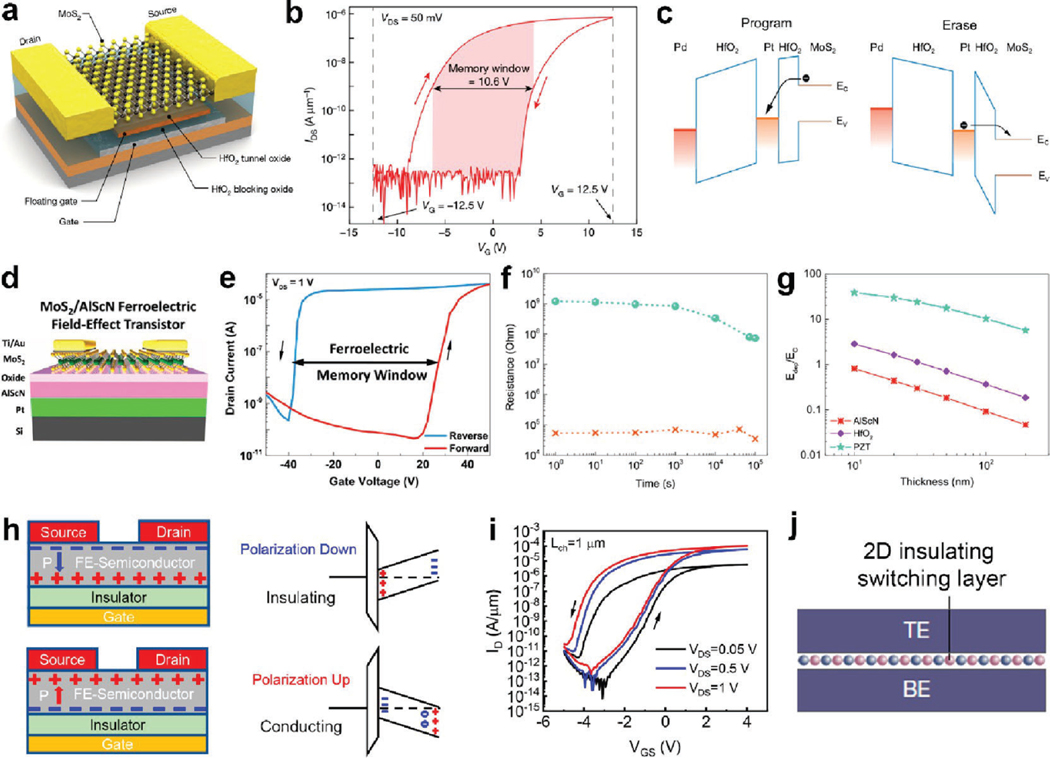

Figure 20.

2D/3D heterojunctions for memory devices. (a) 3D schematic of a FGFETs device based on MOCVD-grown monolayer . (b) Transfer characteristic of the FGFET acquired for two different gate voltage sweep directions, showing a memory window of 10.6 V when observing at 1 nA constant current. (c) Simplified band diagrams of FGFETs for both programming (left panel) and erasing (right panel). Reproduced with permission from ref 374. Copyright 2020 Springer Nature. (d) Schematic view of a FE-FET. (e) Transfer characteristic of the FE-FET acquired for two different gate voltage sweep directions, showing a memory window more than 4 MV/cm. (f) Retention measurement on FE-FET by monitoring the drain current for varying time intervals up to 105 s. (g) Calculated ratio of depolarization field over coercive field in three different FE-FET cases: (1) ; (2) ; (3) . Reproduced with permission from ref 375. Copyright 2020 American Chemical Society. (h) Polarization charges distribution (left) and band diagram (right) in a FeS-FET in polarization down and polarization up states. (i) The demonstrated FeS-FETs showed a high on/off ratio of over 108 and a large memory window of over 1 MV/cm. Reproduced with permission from ref 376. Copyright 2019 Springer Nature. (j) Illustration of an atomristor consisting of a mono or few layer TMD or h-BN sandwiched between conducting electrodes. The structure can produce nonvolatile memory effect. Reproduced with permission from ref 377. Copyright 2019 Springer Nature.