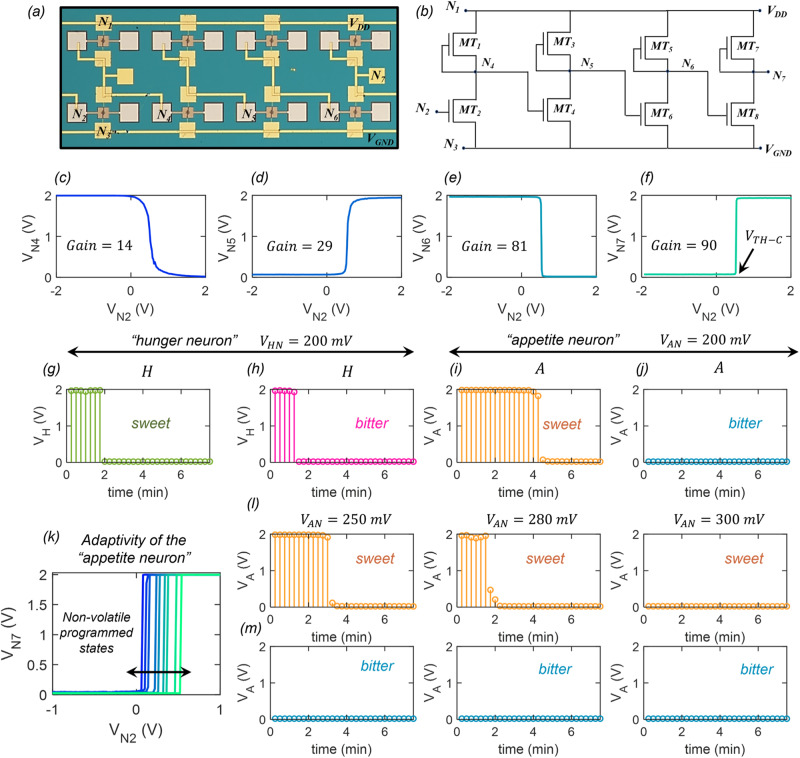

Fig. 4. Monolayer MoS2 memtransistor-based “hunger neuron” and “appetite neuron”.

a Optical image and b circuit schematic of a representative comparator circuit composed of 8 MoS2 memtransistors (–) used as the “hunger neuron” and the “appetite neuron”. The comparator circuit is a 4-stage cascaded inverter as each memtransistor pair, , , , and serve as an inverter. c measured at node, . d measured at node, . e measured at node, , and f measured at node, , as a function of the input voltage, , applied to node . Peak gain for each inverter stage is mentioned in the inset. Highest gain of ~90 is observed for the output stage, which allows for the abrupt state transition for from 0 to , i.e., logic “0” to logic “1”. The input voltage, , at which this sharp state transition occurs is referred to as the comparator threshold (). For the “hunger neuron” and the “appetite neuron”, is represented by and , respectively, and is represented by logic state variables and , respectively. Temporal evolution of , i.e., logic state of in response to g sweet and h bitter taste stimulants. Temporal evolution of , i.e., logic state of in response to i sweet and j bitter taste stimulants. k Transfer curve for the “appetite neuron” for different obtained through non-volatile programming of MoS2 memtransistor, . Corresponding temporal evolution of or in response to l sweet and m bitter taste stimulants.