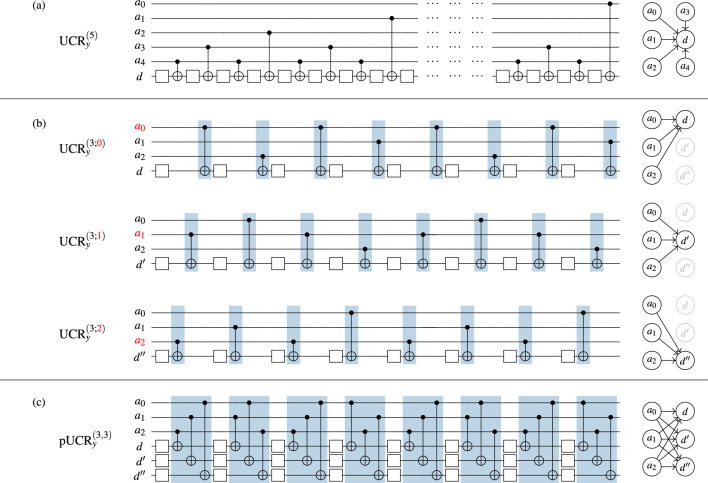

Figure 1.

Different types of uniformly controlled rotation (UCR) gates with optimal connectivity graphs for qubits shown on the right. (a) Standard compact circuit implementation for a gate that was used in the QPIXL framework32 for 5 address and 1 data qubits. Square boxes denote single qubit rotations. (b) All 3 possible realizations of the cyclic permuted UCRs for 3 address and 1 data qubits. (c) Parallel UCR for 3 address and 3 data qubits. The same 3 different permuted circuits using the common 3 address qubits and 3 different data qubits can be reordered to an equivalent circuit with the same CX depth as a single circuit. Blue rectangles indicate groups of 3 CX gates which can be executed concurrently in the same cycle.