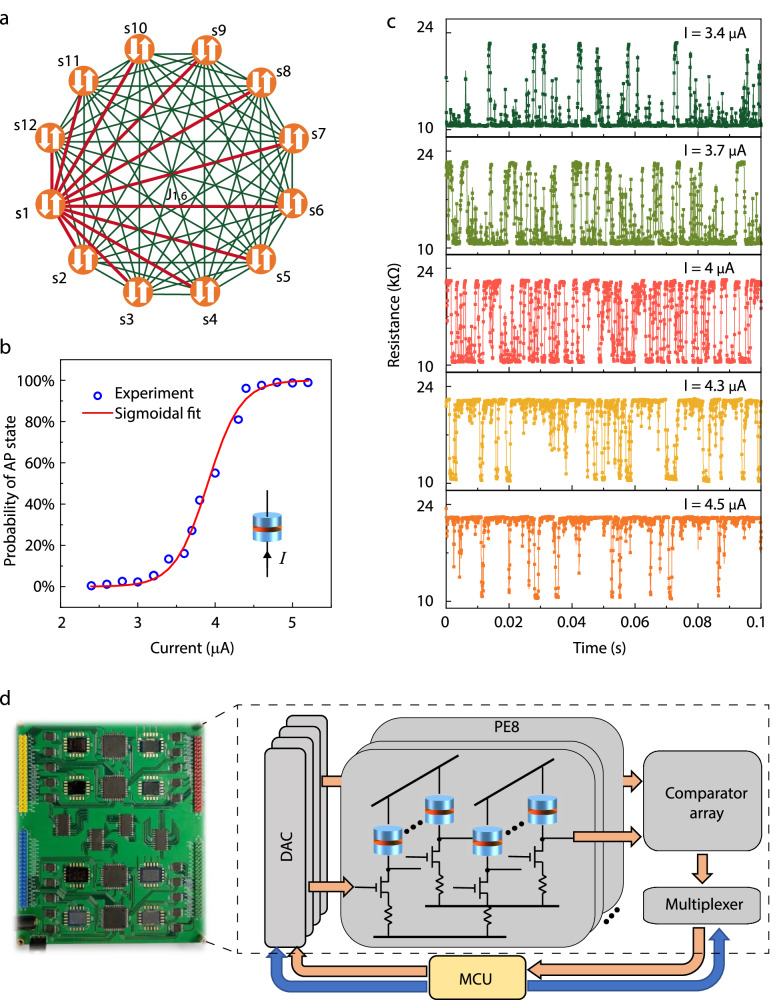

Fig. 1. Illustration of SMTJ-based Ising computer.

a All-to-all connected 12-spin Ising model with s represents the spin and J1,6 represents the coupling between s1 and s6. b Sigmoidal fit of probability of AP state () of an SMTJ under different input currents (I). . Inset: diagram of an SMTJ. A tunneling barrier layer is sandwiched by a reference layer and a free layer. c Time-dependent resistance of an SMTJ under different input currents (I). d Photograph and schematic diagram of SMTJ-based Ising computer. The system contains 8 processing elements (PEs), 4 digital-to-analog converters (DACs), a comparator array, a multiplexer and a microcontroller unit (MCU). Each PE has 10 SMTJ computing units. Each computing unit includes a transistor and a resistor to adjust the property into stochastic. Blue lines and orange arrows represent the control and data flow, respectively.