# Communication Effect of Quasi-One-Dimensional Properties on Source/Drain Contacts in Vertical Nanowire Field-Effect Transistors (VNWFETs)

Iksoo Park<sup>1</sup>, Jaeyong Choi<sup>1</sup>, Jungsik Kim<sup>2</sup>, Byoung Don Kong<sup>1,\*</sup> and Jeong-Soo Lee<sup>1</sup>

- <sup>1</sup> Department of Electrical Engineering, Pohang University of Science and Technology (POSTECH), Pohang 37673, Republic of Korea; isparkk@postech.ac.kr (I.P.); jychoieee@postech.ac.kr (J.C.); ljs6951@postech.ac.kr (J.-S.L.)

- <sup>2</sup> Department of Electrical Engineering, Gyeongsang National University, Jinju 52828, Republic of Korea; jungsik@gnu.ac.kr

- \* Correspondence: bdkong@postech.ac.kr

Abstract: In this study, we investigated the influence of quasi-one-dimensional (Quasi-1D) characteristics on the source and drain contact resistances within vertical nanowire (NW) field-effect transistors (FETs) of diminutive diameter. The top contact of the NW is segregated into two distinct regions: the first encompassing the upper surface, designated as the axial contact, and the second encircling the side surface, known as the radial contact, which is formed during the top-contact metal deposition process. Quantum confinement effects, prominent within Quasi-1D NWs, exert significant constraints on radial transport, consequently inducing a noticeable impact on contact resistance. Notably, in the radial direction, electron tunneling occurs only through quantized, discrete energy levels. Conversely, along the axial direction, electron tunneling freely traverses continuous energy levels. In a meticulous numerical analysis, these disparities in transport mechanisms unveiled that NWs with diameters below 30 nm exhibit a markedly higher radial contact resistance compared to their axial counterparts. Furthermore, an increase in the overlap length (less than 5 nm) contributes to a modest reduction in radial resistance; however, it remains consistently higher than the axial contact resistance.

**Keywords:** quasi-one-dimensional; vertical; nanowire; field-effect transistors; source/drain; contact; quantum confinement; axial contact; radial contact

## 1. Introduction

The relentless miniaturization of transistors has driven the relentless pursuit of advancements to mitigate short-channel effects (SCEs) and bolster transistor performance. Strain engineering, high- $\kappa$ /metal gate (HKMG) materials, and three-dimensional fin fieldeffect transistors (FinFETs) represent some of the key breakthroughs in this ongoing quest [1–3]. FinFETs, leveraging SiGe channels and extreme ultraviolet (EUV) lithography, have successfully achieved scaling down to the 5 nm regime. Gate-all-around (GAA) structures, encompassing nanowires and nanosheets, are actively being explored for technology nodes beyond 5 nm due to their superior gate controllability and enhanced current drivability characteristics [4–6]. Among these innovations, vertical nanowire FETs (VNWFETs) have emerged as a frontrunner for sub-3 nm technology nodes, owing to their inherent advantages in design flexibility and their ability to achieve high-density integration facilitated by the vertical channel fabrication process [7,8].

However, despite the aforementioned advantages, VNWFETs face unique challenges in contact formation.

Unlike conventional transistors, the vertical fabrication process necessitates the creation of separate contacts on both the bottom and top sides of the device. While the bottom contact analysis can use established methods, the top contact demands a more

Citation: Park, I.; Choi, J.; Kim, J.; Kong, B.D.; Lee, J.-S. Effect of Quasi-One-Dimensional Properties on Source/Drain Contacts in Vertical Nanowire Field-Effect Transistors (VNWFETs). *Micromachines* **2024**, *15*, 481. https://doi.org/10.3390/ mi15040481

Academic Editor: Sadia Ameen

Received: 18 February 2024 Revised: 26 March 2024 Accepted: 29 March 2024 Published: 30 March 2024

**Copyright:** © 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). nuanced approach due to its geometrical complexity. It comprises two distinct interfaces: the circular top surface (axial contact) and the surrounding side surface (radial contact), formed during top-contact metal deposition. Addressing these contact formation challenges is paramount to propel VNWFET technology towards practical applications in next-generation electronic devices.

As the width of the nanowire (NW) shrinks, its characteristics transition towards a quasi-one-dimensional (Quasi-1D) regime. Consequently, investigating contact resistance with due consideration for NW dimensions becomes increasingly important [9–12]. Prior studies employed compact modeling to analyze parasitic components within structurally asymmetric VNWFETs, specifically focusing on 10–15 nm nanowires [13]. This modeling approach, which utilized a constant contact resistivity parameter, revealed that the top and bottom electrode asymmetry leads to imbalances in parasitic resistance and capacitance, ultimately impacting device performance. However, as NW dimensions approach the sub-10 nm scale, quantum confinement effects come into play. These effects, including bandgap widening and subband splitting, cause the nanowire's characteristics to deviate significantly from bulk properties, profoundly influencing the contact characteristics at the metal–semiconductor interface [14].

In this study, we used a semi-classical approach that incorporates one-dimensional (1D) quantum effects specific to the top contact structure of VNWFETs. As NW dimensions decrease, the relevant density of states (DOS) exhibits a transition towards Quasi-1D characteristics, distinct from bulk behavior. This phenomenon has a significant impact on the tunneling mechanisms in both the axial and radial directions. By accounting for these quantum confinement effects, we investigated the top contact resistance along both the axial and radial directions. Additionally, we analyzed the influence of overlap distance on the contact resistance. This comprehensive examination aims to shed light on the intricate behavior of VNWFETs, a crucial step towards their continued development and practical implementation in nanoelectronic devices.

#### 2. Modeling of Q1D Transport in Top Contact

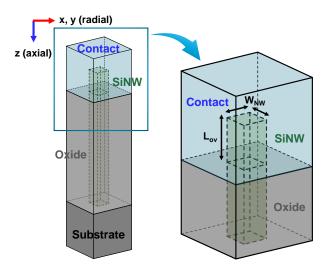

Figure 1 shows a schematic diagram of a vertical nanowire (NW) structure where the top contact comprises two interfaces: one covering the top surface, referred to as the axial contact, and the other covering the side surface with an overlap length  $L_{ov}$ , referred to as the radial contact.

**Figure 1.** A bird's eye view of a schematic diagram depicting a VNWFET and an enlarged view of the top contact structure of the VNWFET.

To take into account the quantum confinement effect of the Si nanowire, the quantized energy states of the NWs can be calculated by solving the Schrödinger equation to determine the discrete energy levels, as expressed by [15]:

$$\mathbf{E}_{c,n} = \frac{\hbar^2 \pi^2 n^2}{m^* \mathbf{W}_{NW}^2},$$

(1)

where  $\hbar$  denotes the reduced Planck constant, *n* represents the quantum number for the confined direction,  $m^*$  is the effective mass of the electron, and  $W_{NW}$  represents the width of the square NW. This equation provides insight into the behavior of electrons within the nanowire, crucial for understanding VNWFET characteristics and optimizing device performance for advanced electronic applications.

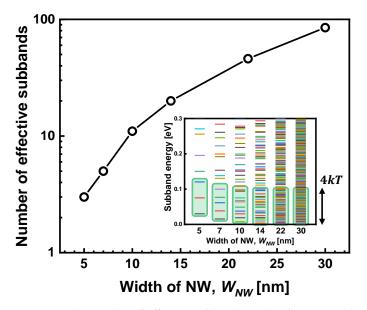

Figure 2 depicts the relationship between the width of the nanowire ( $W_{NW}$ ) and the number of effective subbands it possesses. These subbands are defined as the quantized energy levels within a specific range, encompassing the lowest subband energy ( $E_{c,0}$ ) and extending up to  $E_{c,0} + 4kT$ . The inset of Figure 2 provides a more detailed illustration of these quantized energy levels, calculated using Equation (1) as a function of  $W_{NW}$ . At room temperature, the Fermi–Dirac probability function (f(E)) indicates that approximately 98% of the electrons populate the subbands that fall within the 4kT energy range. Notably, a crucial observation from Figure 2 is the significant decrease in the number of effective subbands that significantly influence electron transport. This number rapidly diminishes to 10 or fewer subbands when the WNW falls below 10 nm.

**Figure 2.** The number of effective subbands in the 4kT energy box from the lowest subband energy. Inset: the calculated subband energy with various widths of nanowire in the 5~30 nm range.

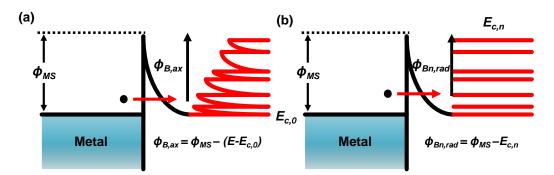

Continuing our analysis with reference to the energy band diagram presented in Figure 3, we can examine the mechanism of electron transport within the nanowire for both the axial and radial contacts. In both cases, electron transport occurs through a process known as field-emission tunneling. Under the assumption that the source/drain (S/D) extension regions are sufficiently doped, the metal–nanowire interface is typically modeled as an Ohmic-like Schottky contact. This assumption is based on the nanowire possessing a sufficiently small width and a doping concentration of  $1 \times 10^{20}$  cm<sup>-3</sup>. However, a critical distinction between the axial and radial contacts arises due to the influence of a parameter stemming from the inherent Quasi-1D quantum effects.

**Figure 3.** Schematic diagrams of an energy band in (**a**) the axial direction and (**b**) the radial direction with the corresponding DOS in a Quasi-1D metal–NW contact.

The density of states (DOS) in the axial direction of the nanowire of each subband energy can be calculated using the following equation [12]:

$$g(E) = \frac{1}{\pi\hbar} \sqrt{\frac{m^*}{2(E - E_{c,n})}},$$

(2)

where *E* is the energy of the electron, and  $E_{c,n}$  are the quantized subband levels. In an NW with a sub-nanometer diameter and significant length, carrier motion is confined to a 1D space. Consequently, carriers traverse a continuous spectrum of energy states along the wire's axis, while their motion in the radial direction is constrained to specific quantized energy levels. In the axial contact, tunneled electrons encounter a continuum of energy levels, whereas along the radial direction, they encounter discrete energy levels. The tunneling probability was calculated using the Wentzel–Kramers–Brillouin (WKB) approximation method, which is expressed as

$$T(E) = exp\left(-\frac{8}{3\hbar}\sqrt{\frac{\epsilon_s m^*}{qN_d}}(\phi_B - V)\right),\tag{3}$$

where  $\epsilon_s$  is the permittivity of the semiconductor,  $N_d$  is the doping concentration of the semiconductor,  $\phi_B$  is the tunneling barrier height, and *V* is the bias voltage.

The tunneling thickness was determined by calculating the depletion width of the metal–semiconductor contact using the formula  $W_d = \sqrt{((2\epsilon_s(\phi_B - V))/(qN_d))}$ , where Fermi-level pinning effects were disregarded due to the specific charge characteristics of one-dimensional nanowires [16]. The tunneling barrier height ( $\phi_B$ ) for both the axial and radial contacts was obtained using Equations (4) and (5), respectively. As shown in Figure 3, electrons encounter distinct barrier heights depending on their transport directions. Those tunneling through the axial direction face a continuum of energy states, suggesting that the axial barrier height is continuous, given by

$$\phi_{B,ax} = \phi_{MS} - (E - E_{c,0}) \tag{4}$$

Those traversing the radial direction face the quantized barrier heights that depend on the quantized levels:

$$\phi_{B_{n,rad}} = \phi_{MS} - E_{c,n} \tag{5}$$

For the metal contacts, titanium was selected, commonly employed as the initial layer in modern CMOS processes, setting the metal–semiconductor work function difference  $(\phi_{MS})$  to 0.3 eV in this scenario.

#### 3. Calculation of Axial and Radial Contact Resistances

Figure 4a shows the contact resistance of the axial ( $R_{ax}$ ) and radial ( $R_{rad}$ ) contacts, determined from the current density calculated using the following equation:

$$J_{S \to M} = qv \int_{E_{c,0}}^{E_{c,0} + 4kT} g(E) f(E) T(E) dE,$$

(6)

where *q* is the electron charge, *v* is the velocity of the electron, *k* is the Boltzmann constant, *T* is the temperature, g(E) is the density of states, f(E) is the Fermi–Dirac distribution probability, and T(E) is the tunneling probability.

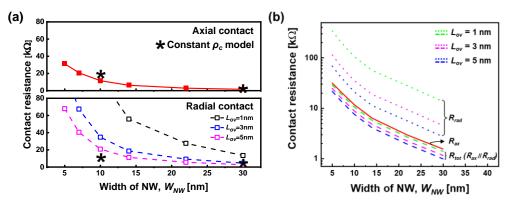

**Figure 4.** (a) Calculated contact resistance of axial ( $R_{ax}$ ) and radial ( $R_{rad}$ ) contacts with varying  $W_{NW}$  and  $L_{ov}$ . The asterisks (\*) denote values calculated using the constant  $\rho_c$  model [13] and (b)  $R_{ax}$  (solid),  $R_{rad}$  (dot), and  $R_{tot}$  (= $R_{ax} || R_{rad}$ ) (dash) with varying  $W_{NW}$  and overlap lengths ( $L_{ov}$  = 1, 3, and 5 nm).

In the case of a 30 nm nanowire width ( $W_{NW}$ ), our proposed approach yields results for the axial contact resistance ( $R_{ax}$ ) and radial contact resistance ( $R_{rad}$ ) that are comparable to those obtained using the previously established constant contact resistivity ( $\rho_c$ ) model, which uses experimentally determined contact resistivity values [13]. This suggests that for larger-diameter NWs, the  $\rho_c$  model can provide a reasonable approximation. However, the  $\rho_c$  model suggests that the radial resistance ( $R_{rad}$ ) can be lowered compared to the axial resistance ( $R_{ax}$ ) by simply adjusting the overlap length ( $L_{ov}$ ). For instance, with an overlap length of 5 nm and  $W_{NW}$  of 10 nm, the  $\rho_c$  model predicts an axial resistance of approximately 20  $\Omega$  and a radial resistance of approximately 10  $\Omega$ . This implies that the total contact resistance can be primarily attributed to the combined effects of both axial and radial resistances. However, for NW diameters below 15 nm, a significant discrepancy emerges between the two models. As previously mentioned, only quantized energy levels are relevant for electron transport in the radial direction. Consequently, the influence of  $W_{NW}$  on radial resistance becomes considerably more pronounced compared to in the axial direction, highlighting the limitations of the pc model for sub-15 nm NWs. Consequently, even with an augmented  $L_{ov}$ ,  $R_{rad}$  consistently maintains higher values than  $R_{ax}$ .

In Figure 4b, the influence of  $R_{ax}$  and  $R_{rad}$  on the total resistance of the top contact,  $R_{tot}$ , is shown. According to our proposed model, due to the quantum confinement effect,  $R_{rad}$  consistently exhibits a larger value compared to  $R_{ax}$  regardless of  $L_{ov}$ . Therefore,  $R_{tot}$  can be represented as the parallel of  $R_{ax}$  and  $R_{rad}$ , confirming that it is primarily determined by  $R_{ax}$ .

### 4. Conclusions

This investigation explores the impact of contact structure on the electrical characteristics of quasi-one-dimensional vertical nanowire field-effect transistors (VNWFETs). These devices feature a distinctive top contact, consisting of two regions: the upper circular area and the circumferential contact encircling the sidewall. Due to the inherent one-dimensional nature of these contact interfaces, they exhibit distinct contact resistance behaviors. The conventional method of calculating contact resistance, based on contact area and specific contact resistivity between the metal and semiconductor, proves inadequate for nanowire contacts with sub-nanometer diameters due to quantum confinement effects. In Quasi-1D VNWFETs, electrons traveling in the radially confined direction encounter strictly quantized energy levels, greatly limiting their tunneling probability compared to the continuous energy states available along the axial direction. Consequently, as nanowire dimensions decrease, electron tunneling in the radial direction experiences a significant reduction in current compared to tunneling along the axial direction. This critical observation underscores the necessity of considering both distinct interface types for effective device performance optimization. Our findings emphasize the crucial need for accurate modeling of quantum confinement effects, particularly in VNWFETs approaching or falling below the 10 nm threshold.

Author Contributions: Conceptualization, I.P.; investigation, I.P. and J.C.; methodology, I.P., J.K. and B.D.K.; data curation, I.P. and J.-S.L.; writing—original draft preparation, I.P. and J.-S.L.; writing—review and editing, I.P., J.-S.L. and B.D.K.; supervision, J.-S.L. and B.D.K. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported by the National R&D Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Science and ICT (2020M3H2A1078045).

**Data Availability Statement:** The data presented in this study are available on request from the corresponding author. The data are not publicly available due to confidentiality request.

**Conflicts of Interest:** The authors declare no conflicts of interest.

#### References

- 1. Chidambaram, P.R.; Bowen, C.; Chakravarthi, S.; Machala, C.; Wise, R. Fundamentals of silicon material properties for successful exploitation of strain engineering in modern CMOS manufacturing. *IEEE Trans. Electron Devices* **2006**, *53*, 944–963. [CrossRef]

- Wu, C.C.; Lin, D.W.; Keshavarzi, A.; Huang, C.H.; Chan, C.T.; Tseng, C.H.; Chen, C.L.; Hsieh, C.Y.; Wong, K.Y.; Cheng, M.L.; et al. High performance 22/20nm FinFET CMOS devices with advanced high-k/metal gate scheme. In Proceedings of the 2010 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 6–8 December 2010.

- Tang, S.H.; Chang, L.; Lindert, N.; Choi, Y.-K.; Lee, W.-C.; Huang, X.; Subramanian, V.; Bokor, J.; King, T.-J.; Hu, C. FinFET-a quasiplanar double-gate MOSFET. In Proceedings of the 2001 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 7 February 2001.

- Bangsaruntip, S.; Cohen, G.M.; Majumdar, A.; Zhang, Y.; Engelmann, S.U.; Fuller, N.C.M.; Gignac, L.M.; Mittal, S.; Newbury, J.S.; Guillorn, M.; et al. High performance and highly uniform gate-all-around silicon nanowire MOSFETs with wire size dependent scaling. In Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009.

- Lauer, I.; Loubet, N.; Kim, S.D.; Ott, J.A.; Mignot, S.; Venigalla, R.; Yamashita, T.; Standaert, T.; Faltermeier, J.; Basker, V.; et al. Si nanowire CMOS fabricated with minimal deviation from RMG FinFET technology showing record performance. In Proceedings of the 2015 Symposium on VLSI Technology, Kyoto, Japan, 16–18 June 2015.

- Mertens, H.; Ritzenthaler, R.; Chasin, A.; Schram, T.; Kunnen, E.; Hikavyy, A.; Ragnarsson, L.-Å.; Dekkers, H.; Hopf, T.; Wostyn, K.; et al. Vertically stacked gate-all-around Si nanowire CMOS transistors with dual work function metal gates. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016.

- Guerfi, Y.; Larrieu, G. Vertical silicon nanowire field effect transistors with nanoscale gate-all-around. Nanoscale Res. Lett. 2016, 11, 210. [CrossRef]

- 8. Veloso, A.; Altamirano-Sánchez, E.; Brus, S.; Chan, B.T.; Cupak, M.; Dehan, M.; Delvaux, C.; Devriendt, K.; Eneman, G.; Ercken, M.; et al. Vertical nanowire FET integration and device aspects. *ECS Trans.* **2016**, *72*, 31–42. [CrossRef]

- 9. Shafizade, D.; Shalcian, M.; Jazaeri, F. Ultrathin junctionless nanowire FET model, including 2-D quantum confinements. *IEEE Trans. Electron Devices* **2019**, *66*, 4101–4106. [CrossRef]

- 10. Svensson, J.; Campbell, E. Schottky barriers in carbon nanotube-metal contacts. J. Appl. Phys. 2011, 110, 111101. [CrossRef]

- 11. Wang, Z.-R.; Zhang, G.; Pey, K.-L.; Tung, C.H.; Lo, P.G.-Q. Schottky-Ohmic transition in metal-all-around electrical nanotubes to silicon nanowires. *J. Appl. Phys.* **2009**, *105*, 094508. [CrossRef]

- 12. Léonard, F.; Talin, A.A. Size-dependent effects on electrical contacts to nanotubes and nanowires. *Phys. Rev. Lett.* **2006**, *97*, 026804. [CrossRef]

- 13. Maheshwaram, S.; Manhas, S.K.; Kaushal, G.; Anand, B.; Singh, N. Vertical nanowire CMOS parasitic modeling and its performance analysis. *IEEE Trans. Electron Devices* **2013**, *60*, 2943–2950. [CrossRef]

- 14. Ma, D.D.D.; Lee, C.S.; Au, F.C.K. Small-diameter silicon nanowire surfaces. Science 2003, 299, 1874–1877. [CrossRef] [PubMed]

- 15. Yoffe, A.D. Low-dimensional systems: Quantum size effects and electronic properties of semiconductor microcrystallites (zero-dimensional systems) and some quasi-two-dimensional systems. *Adv. Phys.* **1993**, *42*, 173–262. [CrossRef]

- 16. Léonard, F.; Tersoff, J. Role of Fermi-level pinning in nanotube Schottky diodes. *Phys. Rev. Lett.* 2000, *84*, 4693. [CrossRef] [PubMed]

**Disclaimer/Publisher's Note:** The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content.