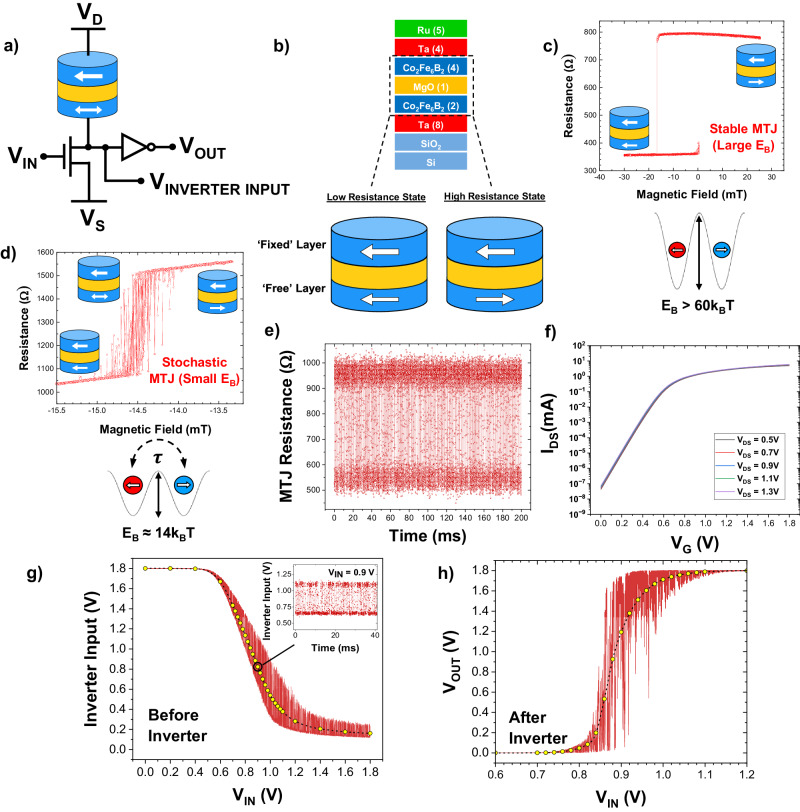

Fig. 1. Implementing probabilistic bits (p-bits) with stochastic magnetic tunnel junctions (MTJs).

a Schematic of the proposed p-bit design, comprised of a stochastic MTJ (magnetic moments represented by the white arrows) connected to the drain of an n-type transistor, forming the stochastic core of the p-bit. The current through the MTJ-transistor pair is determined by the drain (VD) and source (VS) voltages, while the input tunability comes from varying the gate voltage of the transistor (VIN). The inverter is used for thresholding and amplifying the voltage fluctuations between the MTJ and transistor (at VINVERTER INPUT). b Cross-section schematic of a typical MTJ stack, layer thicknesses in nm, and an explanation of the tunnel magnetoresistance (TMR) effect. c Minor loop of a stable MTJ, showing how the resistance changes deterministically as a function of magnetic field for a large energy barrier (EB) free layer (denoted by the representative double-well model where the potential barrier is much larger than ambient thermal energy, kBT). d Minor loop of a stochastic MTJ, showing how the resistance fluctuates between the parallel- and antiparallel state, with a mean dwell time τ, for a small energy barrier-free layer. e Example time-series resistance data for the fluctuating MTJ and f transfer characteristics of the transistor used to obtain the example p-bit’s output. g Graph showing the typical p-bit signal before the inverter’s operation, as a function of the transistor gate voltage (defined as VIN). The average at each point is shown by the dotted line while the inset figure shows example time-series data of the voltage fluctuations at the inverter’s input for VIN = 0.9 V. h Graph showing the typical output of the full p-bit, VOUT, as a function of the input voltage, VIN. The time-averaged signal at each input voltage is represented by the dotted line.