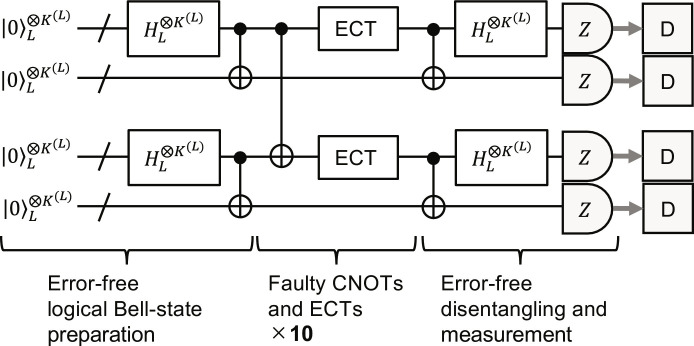

Fig. 10. Simulation of logical CNOT gates.

We first prepare two sets of error-free logical Bell states encoded with the level-L many-hypercube code in four registers. Then, we perform 10 times faulty full transversal logical CNOT gates (implemented by faulty full transversal physical CNOT gates) followed by faulty ECT gadgets on the first and third registers in the circuit-level noise model. Last, we disentangle the logical states by error-free operations and ideally measure all the physical qubits in the Z basis. The measurement outcomes are decoded by the minimum distance decoder. If all the logical outputs are 0, then the 10 sets of full transversal logical CNOT gates succeed and otherwise fail.