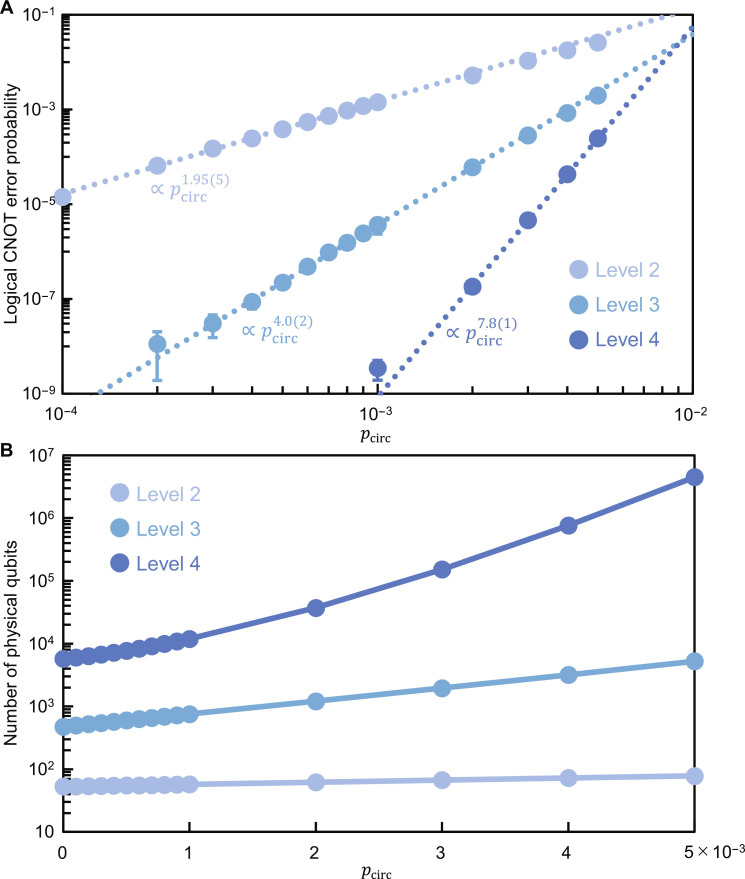

Fig. 6. Performance of full transversal logical CNOT gates for the many-hypercube codes in the circuit-level error model.

(A) Each circle shows the error probability per logical CNOT gate for error rate pcirc. The dotted lines are power-function fits to the five data points from the lowest, from which the exponents are estimated. (B) Total number of physical qubits required for the preparation of a logical all-zero state. See Materials and Methods for the details of the simulation and the main text for the definition of the error model.