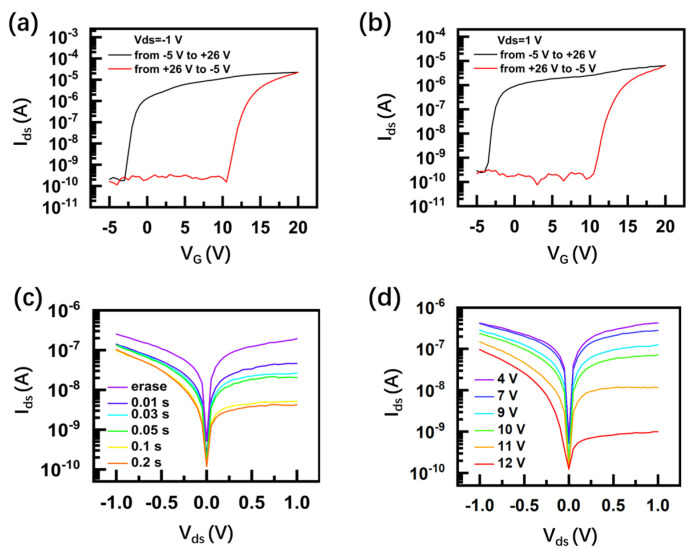

Figure 3.

The dynamic behavior of the nonvolatile gate charge-trap memory based on MoS2/PdSe2 heterostructure: (a,b) Ids–VG characteristics of the device under different VG under the forward bias of −1 V and reverse bias of +1 V, respectively; (c,d) Ids–Vds characteristics of the device under different pulse durations and amplitudes.