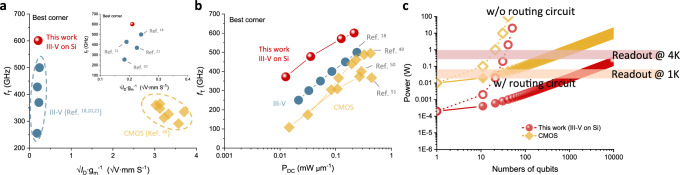

Fig. 5. Achieving high-gain and low-noise cryogenic electronics using III-V on Si devices.

fT versus (a) and fT versus PDC (b) benchmarks for state-of-the-art cryogenic RF transistors. The fT and are extracted at each optimum bias point, not at the same bias. Among the presented devices, our device is closest to the optimum corner region (highest fT and lowest noise indication factor & highest fT and lowest PDC). Inset includes fT versus benchmark only for III-V. Data from refs. 18,20,21,47–50. c Projected power consumption profiles for our device and CMOS depending on the number of gates and considering the presence or absence of routing circuits. The routing ratio is 1-to-10. Colored lines indicate the cooling power achievable with state-of-the-art dilution refrigerators, assuming 50% power consumption at the readout.