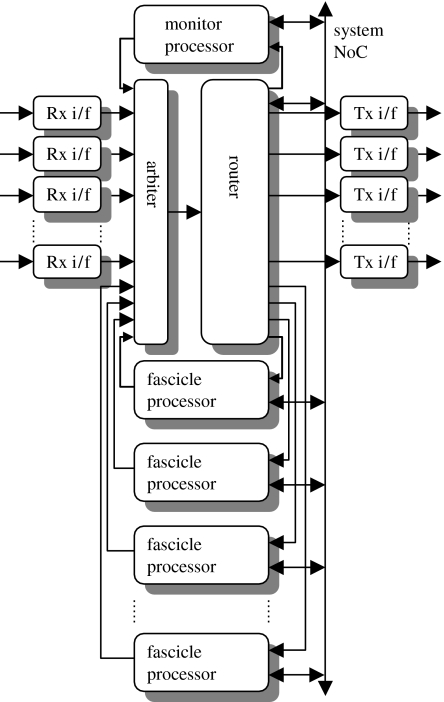

Figure 6.

Organization of a SpiNNaker chip multiprocessor node, illustrating the Communications Network-on-Chip (NoC) that is used to carry spike event packets around the system. Each fascicle processors models many neurons. Packets from other nodes arrive through the receiver interfaces (‘Rx i/f’) and are merged with packets issued by the fascicle processors into a sequential stream by the arbiter. Each packet is then routed to one or several destinations, which may include other processing nodes (via the transmit interfaces—‘Tx i/f’) and/or local fascicle processors. The monitor processor carries out operating system functions and provides visibility to the user of on-chip activity.