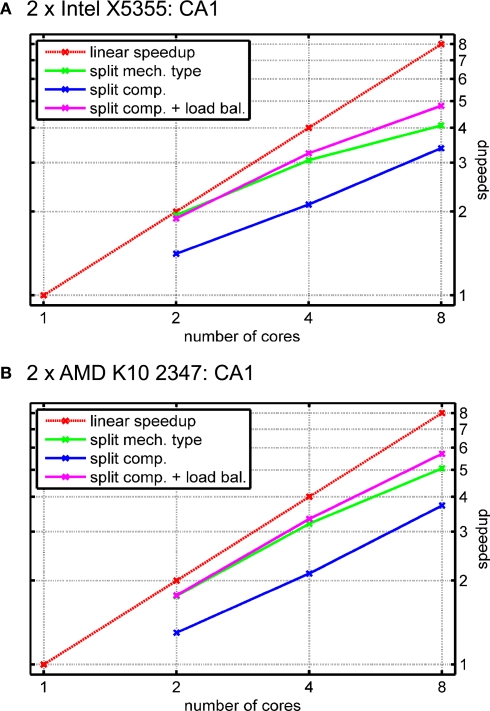

Figure 12.

Simulation of a CA1 pyramidal cell with 600 compartments for 900 ms with a time step length of Δt = 0.025 ms (see Migliore et al., 1999). The cell is split into two equally large pieces; distal dendritic compartments do not use active channels, thus giving a heterogeneous mechanism distribution across the cell. (A) Speedup results on the Intel test system (see Figure 11A). Red line: linear speedup; green: measured speedups of mechanism type level parallelization (Figure 5); blue: compartment level parallelization (Figure 7) without load-balancing for taking into account heterogeneous mechanism distribution across cell; magenta: compartment level parallelization with load-balancing. (B) Same as (A) on the AMD test system (Figure 11C).