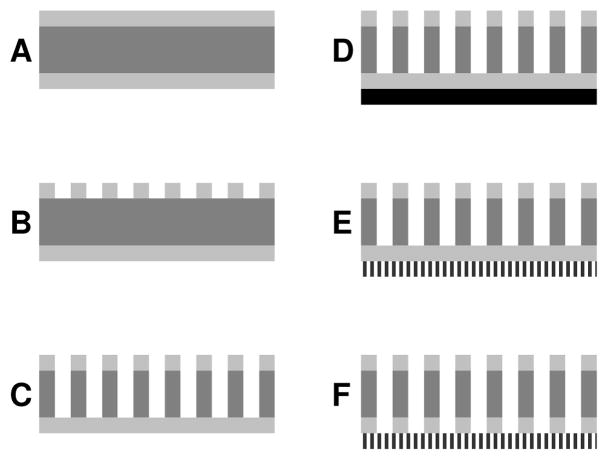

Figure 1.

Fabrication scheme for composite nanoporous membrane. Silicon wafer (dark gray, 100 μm thick) is coated on both sides with low stress silicon nitride (light gray, 40 nm) (A). Si3N4 is patterned via photolithography and reactive ion etching (RIE) (B). Pores are anisotropically dry-etched through Si (C). Triblock copolymer (black, 80 nm) is spin-coated onto top-side Si3N4 and annealed (D). PLA polymer domains are selectively removed by NaOH etching, followed by a brief O2 RIE (E) Si3N4 covering Si pores is removed by hydrofluoric acid etching (F). Note that figures are not drawn to scale.