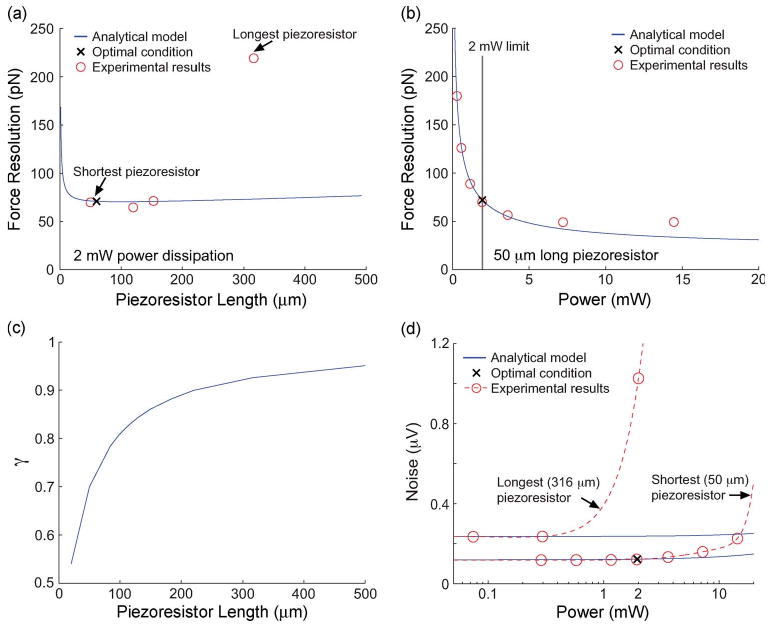

Fig. 11.

Force resolution of an optimal piezoresistive cantilever (Table III) with (a) various piezoresistor lengths and (b) various power dissipations. The optimization technique generated optimal cantilever designs while satisfying the bias voltage (< 2 V) and power dissipation (< 2 mW) constraints. (c) Geometry factor from finite-element method simulation with various piezoresistor lengths. The optimal piezoresistor length shifts from 57 to 120 μm because geometric factor dramatically decreases in short length as the length decreases. We used the same implantation dose in the piezoresistor and interconnects for all devices, but it is preferable to reduce the resistivity of the interconnects to improve the geometry factor. (d) Noise of both short and long piezoresistors (50 and 316 μm) with various power dissipations. Noise deviates from the analytical model, particularly when the piezoresistor is long or the power dissipation is high, and it affects force resolution.