## High- $\kappa$ oxide nanoribbons as gate dielectrics for high mobility top-gated graphene transistors

Lei Liao<sup>a</sup>, Jingwei Bai<sup>b</sup>, Yongquan Qu<sup>a</sup>, Yung-chen Lin<sup>b</sup>, Yujing Li<sup>b</sup>, Yu Huang<sup>b,c,1</sup>, and Xiangfeng Duan<sup>a,c,1</sup>

<sup>a</sup>Department of Chemistry and Biochemistry, <sup>b</sup>Department of Materials Science and Engineering, and <sup>c</sup>California Nanosystems Institute, University of California, Los Angeles, CA 90095

Edited\* by Charles Lieber, Harvard University, Cambridge, MA, and approved February 24, 2010 (received for review December 7, 2009)

Deposition of high- $\kappa$  dielectrics onto graphene is of significant challenge due to the difficulties of nucleating high quality oxide on pristine graphene without introducing defects into the monolayer of carbon lattice. Previous efforts to deposit high-k dielectrics on graphene often resulted in significant degradation in carrier mobility. Here we report an entirely new strategy to integrate high quality high- $\kappa$  dielectrics with graphene by first synthesizing freestanding high- $\kappa$  oxide nanoribbons at high temperature and then transferring them onto graphene at room temperature. We show that single crystalline Al<sub>2</sub>O<sub>3</sub> nanoribbons can be synthesized with excellent dielectric properties. Using such nanoribbons as the gate dielectrics, we have demonstrated top-gated graphene transistors with the highest carrier mobility (up to 23,600  $\text{cm}^2/\text{V} \cdot \text{s}$ ) reported to date, and a more than 10-fold increase in transconductance compared to the back-gated devices. This method opens a new avenue to integrate high-k dielectrics on graphene with the preservation of the pristine nature of graphene and high carrier mobility, representing an important step forward to high-performance graphene electronics.

graphene dielectric integration | carrier mobility | dielectric nanoribbon | nanoelectronics

**G**raphene has attracted considerable interest as a potential electronic material due to its exceptionally high carrier mobility and tunable band gap (1–6). Various strategies have been explored to fabricate field-effect transistors based on graphene or graphene nanostructures (6–13). Most of these efforts to date employ a silicon substrate as a global back gate and silicon oxide as the gate dielectric, which have led to many interesting scientific discoveries, but will be of limited use for practical applications due to the high-gate switching voltage required and the inability to independently address individual devices on the same chip. Top-gated devices with high- $\kappa$  dielectrics can significantly reduce the required switching voltage and readily allow independently addressable device arrays and functional circuits, and therefore are of significant interest (14, 15).

The gate dielectric is an essential component of a transistor, which can significantly impact the critical device parameters including transconductance, subthreshold swing and frequency response. Exploring graphene for future electronics requires effective integration of high quality gate dielectrics, in particular the high- $\kappa$  dielectrics. However, it has been rather challenging to deposit oxide dielectrics onto graphene without introducing defects. The deposition of high- $\kappa$  dielectrics is usually achieved using atomic layer deposition (ALD), which requires reactive surface groups (16–20). Functionalization of graphene surface for ALD either introduces undesired impurities or breaks the chemical bonds in the graphene lattice, inevitably leading to a significant degradation in carrier mobilities (20). Physical vapor deposition (PVD) such as electron-beam evaporation or sputtering process has also been used to deposit dielectrics without the need of surface functionalization. Although the PVD process usually yields lower quality dielectrics and can also cause significant damages to graphene (21, 22). As a result, the mobility values observed in the top-gated devices are typically nearly

one order of magnitude smaller than what can be achieved in the back-gated devices (20–23). Recently, the introducing of polymer or aluminum buffer layer for high- $\kappa$  deposition was demonstrated with improved the device mobility (24, 25), which is still lower than that of the best back-gated graphene devices (1, 4, 5). To eventually realize high-performance graphene-based electronics, alternative approaches must be developed to deposit high quality high- $\kappa$  dielectrics without damaging the pristine graphene.

Here we describe an entirely unique strategy to integrate graphene with high quality high- $\kappa$  dielectrics using free-standing dielectric nanoribbons. Nanoribbons can be synthesized at high temperature with nearly perfect crystalline structure, but manipulated and assembled at room temperature. This flexibility allows the integration of normally incompatible materials and processes and can enable unique functions in electronics or photonics (26–30). In this report, the dielectric properties of aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) nanoribbons are explored for graphene-based electronics. Specifically, high quality dielectric Al<sub>2</sub>O<sub>3</sub> nanoribbons were first synthesized, and then transferred onto graphene as the gate dielectrics for top-gated graphene transistors. This integration approach preserves the pristine nature of the graphene and allows us to achieve the highest room temperature carrier mobility (up to 23,600 cm<sup>2</sup>/V  $\cdot$  s) in top-gated graphene transistors to date.

## **Results and Discussion**

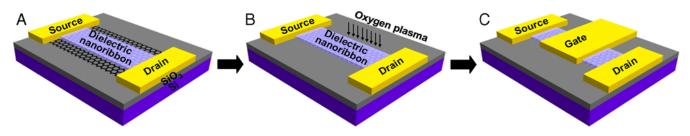

Fig. 1 illustrates our approach to fabricate top-gated graphene transistors. Mechanically peeled graphene flakes on silicon substrate were used as the starting materials in initial studies, although the approach described here can be readily extended to graphene obtained through chemical exfoliation or chemical vapour deposition. Al<sub>2</sub>O<sub>3</sub> nanoribbons were aligned on top of the graphene through a physical dry transfer process (Materials and Methods), followed by e-beam lithography and metallization process to define the source and drain electrodes (Fig. 1A). Oxygen plasma etch was then used to remove the exposed graphene, leaving only the graphene protected underneath the dielectric nanoribbon and the source drain electrodes (Fig. 1B). The top-gate electrode was then fabricated (Fig. 1C). A typical device consists of source, drain and top-gate electrodes (Ti/Au, 50 nm/50 nm), Al<sub>2</sub>O<sub>3</sub> nanoribbon as the top-gate dielectric, a highly doped p-type silicon substrate (< 0.004 ohm  $\cdot$  cm) as the back gate, and a 300 nm thermal silicon oxide layer as the back-gate dielectric.

Aluminum oxide, with a dielectric constant of 9.1, is an important high- $\kappa$  material with excellent dielectric properties, thermal

Author contributions: X.D., Y.H., L.L., and J.B. designed research; L.L. and J.B. performed research; Y.Q., Y.-C.L., and Y.L. contributed new reagents/analytic tools; L.L. and X.D. analyzed data; and L.L., Y.H., and X.D. wrote the paper.

The authors declare no conflict of interest.

<sup>\*</sup>This Direct Submission article had a prearranged editor.

<sup>&</sup>lt;sup>1</sup>To whom correspondence should be addressed. E-mail: xduan@chem.ucla.edu or yhuang@seas.ucla.edu.

This article contains supporting information online at www.pnas.org/cgi/content/full/ 0914117107/DCSupplemental.

**Fig. 1.** Schematic illustration of the fabrication process to obtain top-gated graphene transistors using dielectric oxide nanoribbons as the etching mask and top-gate dielectric. (*A*) A dielectric nanoribbon is aligned on top of graphene using a dry-transfer process without any additional chemical functionalization to minimize the possibility of introducing defects/impurities into the graphene-dielectric interface, and the source-drain electrodes are fabricated by electron-beam lithography. (*B*) Oxygen plasma etch is used to remove the unprotected graphene, leaving only the graphene underneath the dielectric nanoribbon connected to two large graphene blocks underneath the source and drain electrodes. (C) The top-gate electrode is defined through lithography and metallization process.

and chemical stability (30). In our studies,  $Al_2O_3$  nanoribbons were used as an example to demonstrate our concept of using preformed free-standing nanoribbons as the top-gate dielectrics.  $Al_2O_3$  nanoribbons were synthesized through a physical vapor transport approach at 1400 °C (*Materials and Methods*). Transmission electron microscope (TEM) studies show that the  $Al_2O_3$  nanoribbons typically have a width of 1–3 µm, and a length on the order of 10 µm (Fig. 24). Selected area electron

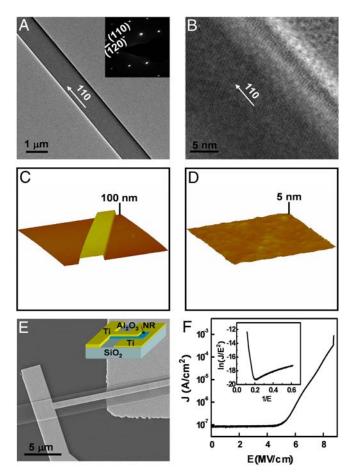

**Fig. 2.** Evaluation of the Al<sub>2</sub>O<sub>3</sub> nanoribbons as dielectric material. (A) TEM image (SAED pattern, *Inset*) and (B) HRTEM image of an Al<sub>2</sub>O<sub>3</sub> nanoribbon show nearly perfect crystalline structure with  $\alpha$ -Al<sub>2</sub>O<sub>3</sub> structure. (C) AFM image of an Al<sub>2</sub>O<sub>3</sub> nanoribbon with thickness approximately 50 nm. The image area is 5  $\mu$ m × 5  $\mu$ m. (D) AFM image of the surface of the Al<sub>2</sub>O<sub>3</sub> nanoribbon, highlighting the smooth surface with a rms roughness <0.2 nm. The image area is 250 nm × 250 nm. (E) The schematic device diagram (*Inset*) and SEM image of an Al<sub>2</sub>O<sub>3</sub> nanoribbon metal-insulator-metal (MIM) device. (F) Current density-electric field (*I-E*) curve of an MIM device made from an Al<sub>2</sub>O<sub>3</sub> nanoribbon, and the inset shows the corresponding (F–N) curve.

diffraction (SAED) study shows the nanoribbon has a single crystalline  $\alpha$ -Al<sub>2</sub>O<sub>3</sub> structure, oriented along  $\langle 110 \rangle$  direction in its long axis, and along  $\langle 001 \rangle$  direction (c-plane) in its thickness (Fig. 2*A* and *Inset*). The high resolution TEM (HRTEM) image confirms that the nanoribbon is a single crystal with nearly perfect crystalline structure free of any obvious defects (Fig. 2*B*). Atomic force microscopy (AFM) studies show that the nanoribbons typically have a thickness around 15–150 nm (Fig. 2*C*), and nearly atomically smooth surface with root mean square roughness <0.2 nm (Fig. 2*D*).

To understand the intrinsic dielectric properties of the nanoribbons, we have fabricated metal-insulator-metal (MIM) devices (Fig. 2*E*) to characterize the current tunnelling, breakdown, and dielectric characteristics. Electrical measurements of the MIM device show that current density (*J*) vs. electric field (*E*) relation exhibits typical Fowler–Nordheim (F–N) tunneling behavior with a breakdown field of 8.5 MV/cm (Fig. 2*F* and *Inset*), comparable to the best quality ALD  $Al_2O_3$  film (31). This type of fieldassisted tunnelling can be described by charge carrier tunnelling through a triangular barrier with

$$J = AE_{\rm OX}^2 \exp(-B/E_{\rm OX})$$

[1]

where

$$4 = 1.54 \times 10^{-6} \left\{ \frac{1}{m^* \Phi_B} \right\},$$

[2]

and

$$B = 6.83 \times 10^7 (m^*)^{1/2} (\Phi_B)^{3/2}.$$

[3]

*J* is current density,  $E_{ox}$  is the oxide electric field, and  $m^*$  is the effective mass of the charge carrier, which is about 0.23 m<sub>e</sub>, and  $\Phi_B$  is the barrier height (31). Fitting the J - E characteristics with the F–N tunnelling model gives a tunnel barrier of about 2.0 eV between Al<sub>2</sub>O<sub>3</sub> and Ti, comparable to previous reports of the barrier height between ALD Al<sub>2</sub>O<sub>3</sub> and metals of similar work function (31, 32). The relative dielectric constant is also determined from capacitance-voltage measurement as 8.5, which is larger than typical values observed in ALD Al<sub>2</sub>O<sub>3</sub> films (31). These studies clearly demonstrate that the Al<sub>2</sub>O<sub>3</sub> nanoribbons have dielectric properties comparable to or better than the best quality ALD Al<sub>2</sub>O<sub>3</sub> film (31), and can function as an excellent dielectric material for top-gated graphene transistors.

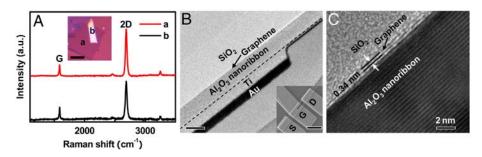

The  $Al_2O_3$  nanoribbons can be aligned onto the top of the graphene through a physical transfer process (*Materials and Methods*). Previous studies have shown that the deposition of oxide on top of graphene often introduces significant defects into the graphene structure with an obvious defect band (D-band) emerging around 1350 cm<sup>-1</sup> in Raman spectra. To this end, we have employed micro-Raman spectroscopy to investigate the interaction between an  $Al_2O_3$  nanoribbon and the underlying graphene (Fig. 3A and Inset). Micro-Raman spectra were

**Fig. 3.** Characterization of the graphene/ $Al_2O_3$  nanoribbon interface. (*A*) Raman spectra of the graphene with (*Point b*) and without (*Point a*)  $Al_2O_3$  nanoribbon covering. The inset shows the optical image of an  $Al_2O_3$  nanoribbon on graphene, the scale bar is 2  $\mu$ m. There is no D-band in either spectrum, indicating that  $Al_2O_3$  nanoribbon does not introduce any appreciable defects into graphene lattice. (*B*) A cross-section TEM image of the top-gate stack, the scale bar is 100 nm. The inset shows an SEM image of a typical device, the scale bar indicates 5  $\mu$ m. The dotted line in the inset shows the cross-section cutting direction. (*C*) A cross-section HRTEM image of the interface between  $Al_2O_3$  nanoribbon and a trilayer graphene. The partially incomplete grahene layers in the image are caused by electron-beam damage during the TEM imaging process.

collected from bare graphene (*Point a*) and  $Al_2O_3$  nanoribbon covered graphene (*Point b*). Significantly, there is no clear difference between two Raman spectra and there is no obvious D-band (Fig. 3*A*), in contrast to previous studies where an obvious D-band is observed (33).

The excellent dielectric properties observed in the single crystalline  $\alpha$ -Al<sub>2</sub>O<sub>3</sub> nanoribbons readily allows us to employ them as the gate dielectrics for top-gated graphene transistors (Fig. 3*B* and *Inset*). Cross-section TEM was used to study the graphene–dielectric interface (Fig. 3 *B* and *C*). The gate stack (SiO<sub>2</sub>/graphene/Al<sub>2</sub>O<sub>3</sub>/Ti/Au) could be observed in Fig. 3*B*. The HRTEM image of the device shows that the graphene layers are intimately integrated with the crystalline Al<sub>2</sub>O<sub>3</sub> nanoribbon without any obvious gap or impurities between them (Fig. 3*C*). Together, these studies clearly demonstrate that the physical assembly approach can effectively integrate Al<sub>2</sub>O<sub>3</sub> nanoribbon with graphene lattice, and thus can effectively preserve the high carrier mobility in the resulting devices.

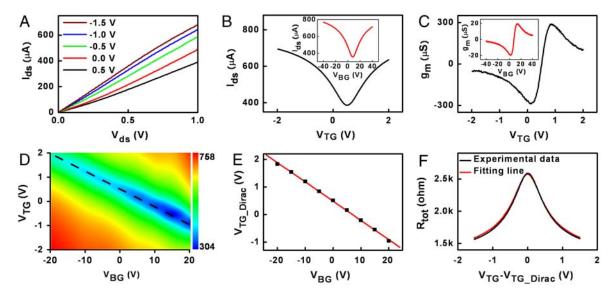

The electrical transport studies of the top-gated graphene transistors were carried out at room temperature. Fig. 4*A* shows the drain-source current ( $I_{ds}$ ) versus drain-source voltage ( $V_{ds}$ ) output characteristics of the transistor at various top-gate voltage

(V<sub>TG</sub>) of -1.5, -1.0, -0.5, 0.0, and 0.5 V. The device delivers an on current of 675  $\mu$ A at V<sub>ds</sub> = 1 V and V<sub>g</sub> = -1.5 V. To evaluate the top-gated devices versus standard back-gated devices, we have measured the transfer characteristics,  $I_{ds}$  versus top-gated voltage (V<sub>TG</sub>) and back-gated voltage (V<sub>BG</sub>) (Fig. 4B and *Inset*). Significantly, the required gate voltage swing to achieve similar current modulation in top-gate configuration is >1 order of magnitude smaller than that in back-gate configuration. The transconductance  $g_m = \frac{dI_{ds}}{dV_{TG}}$  can be extracted from the  $I_{ds}$ -V<sub>TG</sub> curve (Fig. 4C). At V<sub>ds</sub> = 1 V, the top-gated device exhibits a max  $g_m$  of about 290  $\mu$ S, which is about 15 times larger than that of the back-gated configuration ( $g_m \sim 19.5 \mu$ S).

Fig. 4D further shows two-dimensional plot of the device conductance as a function of varying  $V_{BG}$  and  $V_{TG}$  bias, from which we can determine the top-gate Dirac point ( $V_{TG_{Dirac}}$ ) shift as a function of  $V_{BG}$  (Fig. 4*E*). It gives the ratio between top-gate and back-gate capacitances,  $C_{TG}/C_{BG} \approx 14.3$ . This gate capacitance ratio is consistent with the improvement factor (approximately 15) in transconductance of top- versus back-gated configurations. Using the back-gate capacitance value of  $C_{BG} = 11.5 \text{ nF/cm}^2$ , the top-gate capacitance is estimated to be  $C_{TG} = 164.5 \text{ nF/cm}^2$ , corresponding to a relative dielectric

**Fig. 4.** Room temperature electrical properties of the top-gated graphene device using  $Al_2O_3$  nanoribbon as the gate dielectric. (*A*)  $I_{ds}$ -V<sub>ds</sub> output characteristics, the channel width and length of the device is 2.1 µm and 4.1 µm. (*B*) Transfer characteristics at  $V_{ds} = 1$  V for the device using top and back gate (*Inset*). (*C*) Transconductance  $g_m$  as a function of top-gate voltage  $V_{TG}$ , the inset shows the  $g_m$  vs.  $V_{BG}$ . The plots indicate the top gate  $g_m$  is about 15 times higher than the back-gate  $g_m$ . (*D*) Two-dimensional plot of the device conductance at varying  $V_{BG}$  and  $V_{TG}$  bias. The unit in the color scale is µS. (*E*) The top-gate Dirac point  $V_{TG_{Dirac}}$  at different  $V_{BG}$ . (*F*) Experimental plot (*Black Line*) and modeling fitting (*Red Line*) of  $R_{tot}$  vs.  $V_{TG}$ - $V_{TG_{Dirac}}$  relation to derive the contact resistance and carrier mobility.

Table 1. The mobility values observed in multiple top-gate graphene transistors with variable Al<sub>2</sub>O<sub>3</sub> thickness.

| Device No.           | 1     | 2     | 3     | 4     | 5     | 6     | 7     | 8     | 9     |

|----------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Thickness (nm)       | 38    | 45    | 48    | 50    | 60    | 65    | 75    | 82    | 150   |

| Mobility (cm²/V · s) | 23600 | 22400 | 18200 | 22600 | 11200 | 15300 | 21100 | 11800 | 13300 |

constant of 8.4 for  $Al_2O_3$  nanoribbon, which is also consistent with the value obtained from MIM devices.

To further gauge the transistor performance, it is important to determine the carrier mobility. To accurately derive the mobility value, it is necessary to exclude the contact resistance that is comparable to the graphene transistor channel resistance. The total resistance of the device can be expressed as the following (25):

$$R_{\text{tot}} = R_{\text{contact}} + R_{\text{channel}} = R_{\text{contact}} + \frac{L/W}{ne\mu}.$$

[4]

Where  $R_{\text{channel}}$  is the resistance of the graphene channel covered by top-gate electrode, the contact resistance  $R_{\text{contact}}$  consists of the uncovered graphene section resistance and the metal/ graphene contact resistance, L is the channel length, W is the channel width, and *n* is the carrier concentration in the graphene channel region, and can be approximated by the following equation

$$n = \sqrt{n_0^2 + n_{\rm TG}^2} = \sqrt{n_0^2 + ((C_{\rm TG}(V_{\rm TG} - V_{\rm TG_{\rm Dirac}})/e)^2}$$

[5]

where  $n_0$  is the residual carrier concentration, representing the density of carriers at Dirac point (34);  $n_{\text{TG}} = C_{\text{TG}}(V_{\text{TG}} - V_{\text{TG}_{\text{Dirac}}})/e$  is the carrier concentration induced by the top-gate bias away from the Dirac point,  $C_{\text{TG}}$  can be approximated by the oxide capacitance of 164.5 nF cm<sup>-2</sup> (the quantum capacitance is neglected here as it is >1 order of magnitude larger approximately 2000 nF cm<sup>-2</sup>).

By fitting this model to the measured data in Fig. 4B, we can extract the relevant parameters,  $n_0$ ,  $R_{\text{contact}}$  and  $\mu$ . Fig. 4F shows the measured  $R_{tot}$  versus  $V_{TG}$  (Black Line), along with the fitted curve derived from Eq. 4 (Red Line). The fitted curve agrees well with the experimental data, with a single value of the residual concentration  $n_0 = 4.1 \times 10^{11} \text{ cm}^{-2}$ ,  $\tilde{R_{\text{contact}}} = 1240 \Omega$ , and the mobility  $\mu = 22,400 \text{ cm}^2/\text{V} \cdot \text{s}$ , which represents the highest carrier mobility value observed in top-gated graphene devices to date. The fitted contact resistance  $R_{\text{contact}} = \sim 1240 \ \Omega$  is comparable to the  $R_{\text{contact}}$  determined by four-probe measurements of similar devices (Fig. S1). The mobility value derived from top-gated configuration is also consistent with that obtained from back-gated measurement (25,600 cm<sup>2</sup>/V  $\cdot$  s). We have studied multiple devices fabricated with the same approach, all of which exhibited carrier mobilities well exceeding  $10,000 \text{ cm}^2/\text{V} \cdot \text{s}$ (Table 1), comparable to the best reported values in back-gated devices and about one order of magnitude better than typical values previously reported for top-gated devices (17, 20, 21). The variation in mobility values is commonly seen in graphene-based devices (35), which may be attributed to variable local environment with different local potential, defects, impurities, or stress. Together, these studies clearly demonstrate that the presence of Al<sub>2</sub>O<sub>3</sub> nanoribbon on top of graphene does not lead to any mobility degradation, in contrast to previous efforts in using ALD or PVD to deposit dielectrics on graphene.

## Conclusions

In conclusion, a unique strategy has been demonstrated to integrate pristine graphene with high quality high- $\kappa$  dielectrics by physically assembling free-standing oxide nanoribbons. Using the Al<sub>2</sub>O<sub>3</sub> nanoribbons as the gate dielectrics, the top-gated graphene transistors have been fabricated to exhibit superior performance with the highest carrier mobility observed in top-gated device to date. This method opens a unique avenue to integrate high- $\kappa$  dielectrics on graphene with the preservation of high carrier mobility. With further optimization of nanoribbon growth and assembly process to precisely control their physical dimension and spatial location (36–40), large arrays of top-gated graphene transistors or circuits can be envisioned. This physical assembly and integration approach can thus open a unique avenue to high-performance graphene electronics to impact broadly from high frequency high speed circuits to flexible electronics.

## **Materials and Methods**

Synthesis of Al<sub>2</sub>O<sub>3</sub> Nanoribbons. Aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) nanoribbons were synthesized through a physical vapor transport approach at 1400 °C. To grow Al<sub>2</sub>O<sub>3</sub> nanoribbons, aluminum, and nanometer-sized Al<sub>2</sub>O<sub>3</sub> powders with a molar ratio of 4:1 were used as the starting materials. The ceramic boat with the mixture was placed at the center of a horizontal tube furnace and an alumina piece was placed at the downstream as the deposition substrate. The temperature was raised to target temperature with a flow of 400 sccm Ar as the carrying gas. The temperature was maintained for 1 h and then naturally cooled to the room temperature.

**Dry Transfer of Al<sub>2</sub>O<sub>3</sub> Nanoribbons.** The overall process involves physical transfer of Al<sub>2</sub>O<sub>3</sub> nanoribbons directly from a Al<sub>2</sub>O<sub>3</sub> nanoribbon growth substrate to a graphene substrate via contact printing. Specifically, a graphene device substrate is first firmly attached to a benchtop, and the Al<sub>2</sub>O<sub>3</sub> nanoribbon growth substrate is placed upside down on top of the graphene substrate so that the Al<sub>2</sub>O<sub>3</sub> nanoribbons are in contact with the graphene. A gentle manual pressure is then applied from the top followed by slightly sliding the growth substrate. The Al<sub>2</sub>O<sub>3</sub> nanoribbons are aligned by sheer forces during the sliding process. The sliding process results in direct dry transfer of nanoribbons from the growth substrate to the desired graphene substrate. The sample is then rinsed with isopropanol followed by nitrogen blow-dry, in which the capillary drying process near the Al<sub>2</sub>O<sub>3</sub> nanoribbons can help the Al<sub>2</sub>O<sub>3</sub> nanoribbons to be firmly attached to the substrate surface.

**Characterization of Al<sub>2</sub>O<sub>3</sub> Nanoribbons, Device Fabrication, and Measurements.** The microstructures and morphologies of the Al<sub>2</sub>O<sub>3</sub> nanoribbons were characterized by a JEOL 6700 SEM. The lattice image of the Al<sub>2</sub>O<sub>3</sub> nanoribbons was observed by an FEI Titan HRTEM. The thickness was measured using atomic force microscope (AFM, Veeco Dimension 5000). Oxygen plasma (Diener Electronic) was used to selectively etch away the unprotected graphene region and leave graphene ribbons underneath the Al<sub>2</sub>O<sub>3</sub> nanoribbon mask protection. The etch time is about 160 s at a power level of 40 W. The electrical transport properties were measured by a Lakeshore probe station with home built data acquisition system

ACKNOWLEDGMENTS. We acknowledge the Electron Imaging Center for Nanomachines at the University of California Los Angeles for the technical support of TEM, Nanoelectronics Research Facility at the University of California Los Angeles for technical support of device fabrication. This work was supported by the Henry Samueli School of Engineering and an Applied Science Fellowship (Y.H.), and by the National Institutes of Health Director's New Innovator Award Program, part of the National Institutes of Health Roadmap for Medical Research Grant 1DP2OD004342-01 (X.D.).

2. Bunch JS, Yaish Y, Brink M, Bolotin K, McEuen PL (2005) Coulomb oscillations and Hall effect in quasi-2D graphite quantum dots. *Nano Lett* 5:287–290.

<sup>1.</sup> Novoselov KS, et al. (2004) Electric field effect in atomically thin carbon films. *Science* 306:666–669.

- Novoselov KS, et al. (2005) Two-dimensional gas of massless Dirac fermions in graphene. Nature 438:197–200.

- Zhang YB, Tan YW, Stormer HL, Kim P (2005) Experimental observation of the quantum Hall effect and Berry's phase in graphene. *Nature* 438:201–204.

- Bolotin KI, et al. (2008) Ultrahigh electron mobility in suspended graphene. Solid State Commun 146:351–355.

- Avouris P, Chen ZH, Perebeinos V (2007) Carbon-based electronics. Nat Nanotechnol 2:605–615.

- 7. Chen ZH, Lin YM, Rooks MJ, Avouris P (2007) Graphene nano-ribbon electronics. *Physica E* 40:228–232.

- Han MY, Ozyilmaz B, Zhang YB, Kim P (2007) Energy band-gap engineering of graphene nanoribbons. *Phys Rev Lett* 98:206805.

- Li XL, Wang XR, Zhang L, Lee SW, Dai HJ (2008) Chemically derived, ultrasmooth graphene nanoribbon semiconductors. *Science* 319:1229–1232.

- Wang XR, et al. (2008) Room-temperature all-semiconducting sub-10-nm graphene nanoribbon field-effect transistors. Phys Rev Lett 100:206803.

- 11. Bai JW, Duan XF, Huang Y (2009) Rational fabrication of graphene nanoribbons using a nanowire etch mask. *Nano Lett* 9:2083–2087.

- Jiao LY, Zhang L, Wang XR, Diankov G, Dai HJ (2009) Narrow graphene nanoribbons from carbon nanotubes. Nature 458:877–880.

- Kosynkin DV, et al. (2009) Longitudinal unzipping of carbon nanotubes to form graphene nanoribbons. Nature 458:872–875.

- Javey A, et al. (2002) High-kappa dielectrics for advanced carbon-nanotube transistors and logic gates. Nat Mater 1:241–246.

- Wind SJ, Appenzeller J, Martel R, Derycke V, Avouris P (2002) Vertical scaling of carbon nanotube field-effect transistors using top gate electrodes. *Appl Phys Lett* 80:3817–3819.

- Lee BK, et al. (2008) Conformal Al<sub>2</sub>O<sub>3</sub> dielectric layer deposited by atomic layer deposition for graphene-based nanoelectronics. *Appl Phys Lett* 92:203102.

- Meric I, et al. (2008) Current saturation in zero-bandgap, topgated graphene fieldeffect transistors. Nat Nanotechnol 3:654–659.

- Wang XR, Tabakman SM, Dai HJ (2008) Atomic layer deposition of metal oxides on pristine and functionalized graphene. J Am Chem Soc 130:8152–8153.

- Xuan Y, et al. (2008) Atomic-layer-deposited nanostructures for graphene-based nanoelectronics. Appl Phys Lett 92:013101.

- Lin YM, et al. (2009) Operation of graphene transistors at gigahertz frequencies. Nano Lett 9:422–426.

- 21. Lemme MC, Echtermeyer TJ, Baus M, Kurz H (2007) A graphene field-effect device. IEEE Electr Device L 28:282–284.

- Wang HM, Wu YH, Ni ZH, Shen ZX (2008) Electronic transport and layer engineering in multilayer graphene structures. *Appl Phys Lett* 92:053504.

- Liao L, Bai J, Qu Y, Huang Y, Duan X (2010) Single-layer graphene on Al<sub>2</sub>O<sub>3</sub>/Si substrate: Better contrast and higher performance of graphene transistors. *Nanotechnology* 21:015705.

- Farmer DB, et al. (2009) Utilization of a buffered dielectric to achieve high field-effect carrier mobility in graphene transistors. Nano Lett 9:4474–4478.

- Kim S, et al. (2009) Realization of a high mobility dual-gated graphene field-effect transistor with Al<sub>2</sub>O<sub>3</sub> dielectric. Appl Phys Lett 94:053504.

- Pan ZW, Dai ZR, Wang ZL (2001) Nanobelts of semiconducting oxides. Science 291:1947–1949.

- Comini E, Faglia G, Sberveglieri G, Pan ZW, Wang ZL (2002) Stable and highly sensitive gas sensors based on semiconducting oxide nanobelts. *Appl Phys Lett* 81:1869–1871.

- Arnold MS, Avouris P, Pan ZW, Wang ZL (2003) Field-effect transistors based on single semiconducting oxide nanobelts. J Phys Chem B 107:659–663.

- 29. Duan XF (2007) Assembled semiconductor nanowire thin films for high-performance flexible macroelectronics. *MRS Bull* 32:134–141.

- Law M, et al. (2004) Nanoribbon waveguides for subwavelength photonics integration. Science 305:1269–1273.

- 31. Groner MD, Elam JW, Fabreguette FH, George SM (2002) Electrical characterization of thin  $Al_2O_3$  films grown by atomic layer deposition on silicon and various metal substrates. *Thin Solid Films* 413:186–197.

- Afanas'ev VV, Houssa M, Stesmans A, Adriaenssens GJ, Heyns MM (2002) Band alignment at the interfaces of Al<sub>2</sub>O<sub>3</sub> and ZrO<sub>2</sub>-based insulators with metals and Si. J Non-Cryst Solids 303:69–77.

- Ni ZH, et al. (2008) Tunable stress and controlled thickness modification in graphene by annealing. ACS Nano 2:1033–1039.

- Adam S, Hwang EH, Galitski VM, Das Sarma S (2007) A self-consistent theory for graphene transport. Proc Natl Acad Sci USA 104:18392–18397.

- Tan YW, et al. (2007) Measurement of scattering rate and minimum conductivity in graphene. *Phys Rev Lett* 99:246803.

- Huang Y, Duan X, Wei QQ, Lieber CM (2001) Directed assembly of one dimensional nanostructures into functional networks. *Science* 291:630–633.

- Whang D, Jin S, Wu Y, Lieber CM (2003) Large-scale hierarchical organization of nanowire arrays for integrated nanosystems. *Nano Lett* 3:1255–1259.

- Tao A, et al. (2003) Langmuir-Blodgett silver nanowire monolayers for molecular sensing using surface-enhanced Raman spectroscopy. Nano Lett 3:1229–1233.

- 39. Duan X, et al. (2003) High-performance thin-film transistors using semiconductor nanowires and nanoribbons. *Nature* 425:274–278.

- 40. Rogers JA, Nuzzo RG (2005) Recent progress in soft lithography. Mater Today 8:50-56.