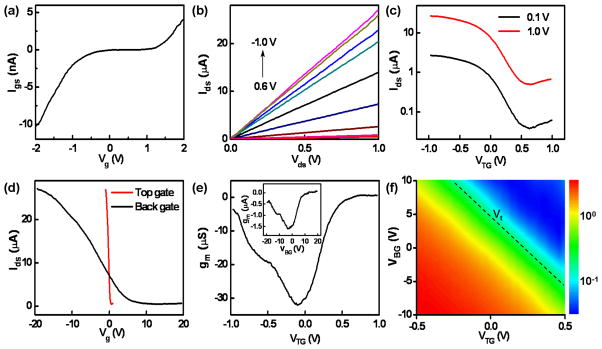

Fig. 4.

Room temperature electrical properties of the top-gated GNR device by using Si/HfO2 coreshell nanowire as the top-gate. (a) Gate leakage current versus top-gate voltage. The leakage current is negligible within ± 1 V range. (b) Ids-Vds output characteristics at variable top-gate voltage starting from 0.6 V at bottom to −1.0 V at top in the step of −0.2 V. (c) The transfer characteristics Ids-VTG at Vds = 0.10 and 1.0 V. (d) Ids-VTG and Ids-VBG transfer characteristics at Vds = 1 V. (e) Transconductance as a function of top-gate voltage VTG and back gate voltage VBG (inset). (f) Two-dimensional plot of the device conductance at varying VBG and VTG bias, the unit in the colour scale is μS.