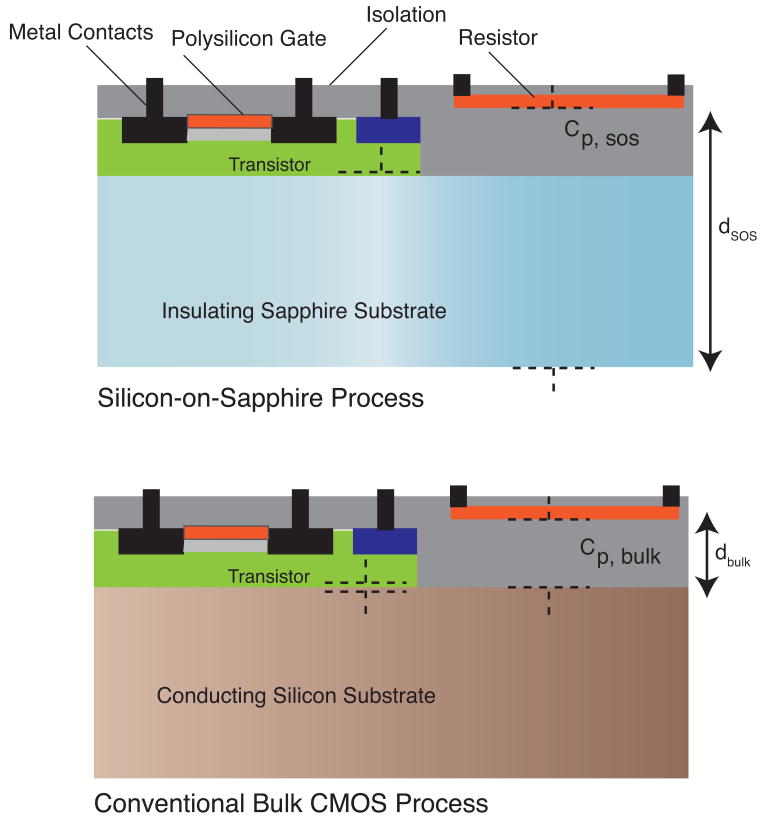

Figure 3.

The patch-clamp system was implemented using silicon-on-sapphire (SOS) technology. The insulating substrate in SOS (top) reduces parasitic capacitance and allows fabrication of large resistors to implement Rf with no degradation in frequency response. The insulating substrate reduces crosstalk between channels and allows devices to operate at faster speeds than conventional bulk CMOS technology (bottom).