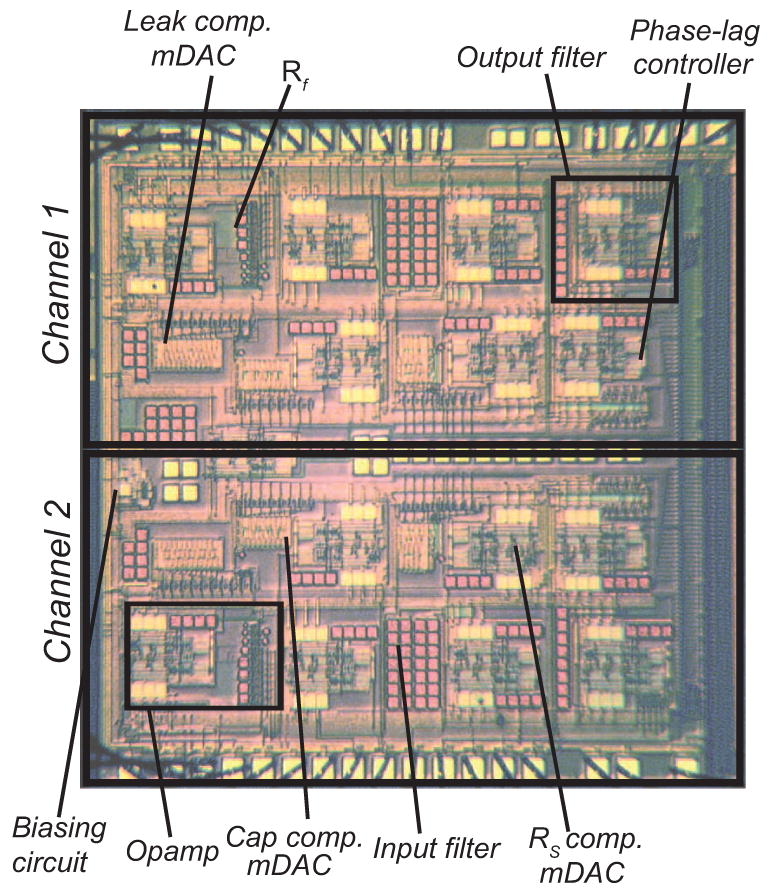

Figure 4.

A micrograph of the test circuit in silicon-on-sapphire technology. The fabricated die contained two channels and occupied just 3 × 3mm2. Each channel has series resistance, parasitic capacitance and leak compensation capability. After initial setup expenditures, each amplifier costs just a few dollars to manufacture.