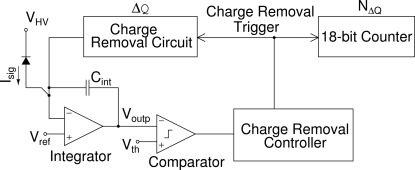

Figure 1.

A high-level schematic of the pixel architecture. Photo-charge (I sig) from the reverse-biased diode is integrated across C int. When the comparator senses a near-to-overflow condition, a charge removal operation, which increments a count in the 18-bit counter, is triggered. The pixel output at the end of an exposure is the combination of the digital counts (N ΔQ) and the analog residual (V outp) (Schuette, 2008 ▶).