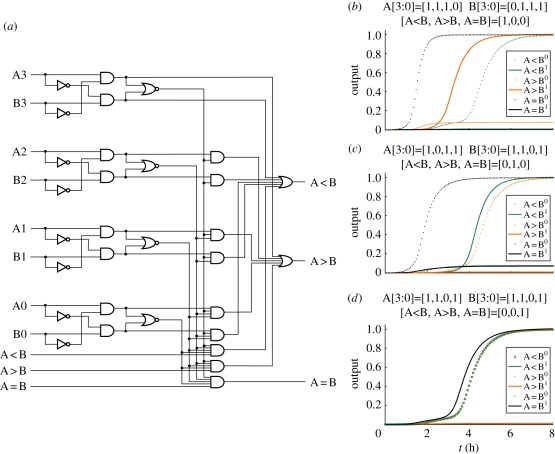

Figure 5.

A 74L85 standard 4-bit magnitude comparator (four layers deep) and its seesaw circuit simulation, with 1x = 50 nM. (a) The digital logic circuit diagram. The corresponding seesaw circuit has roughly 100 seesaw gates. (b) Seesaw circuit simulation with selected input vector of A greater than B. (c) Seesaw circuit simulation with selected input vector of A smaller than B. (d) Seesaw circuit simulation with selected input vector of A equal to B.