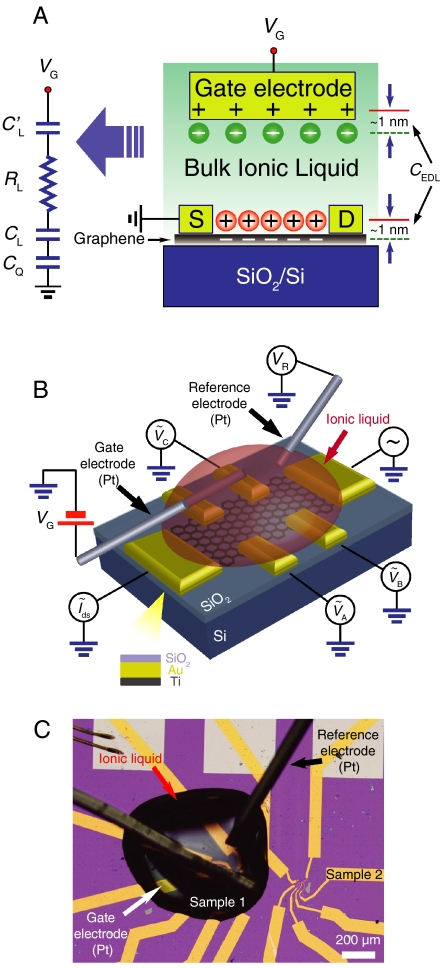

Fig. 1.

Electric double-layer graphene devices. (A) A schematic cross-section of our graphene EDLTs, together with the equivalent electrical circuit describing its operation. In the equivalent circuit,  is the capacitance between Pt gate and liquid, RL is the electrical resistance of the bulk of the ionic liquid, where transport is mediated by ions, CL and CQ, are the geometrical capacitance of double layer/graphene interface and the quantum capacitance of graphene associated with the finite density of states. (B) A schematic representation of a device including the bias configuration used in the electrical measurements. (C) Optical microscope image of an actual device (the white bar in the right bottom corner is 200 μm long). In fact, two separate graphene flakes are visible on the substrate, but only one of them is immersed in the ionic liquid. Also clearly visible are the two Pt wires immersed in the ionic liquid, acting as gate and quasi-reference electrodes.

is the capacitance between Pt gate and liquid, RL is the electrical resistance of the bulk of the ionic liquid, where transport is mediated by ions, CL and CQ, are the geometrical capacitance of double layer/graphene interface and the quantum capacitance of graphene associated with the finite density of states. (B) A schematic representation of a device including the bias configuration used in the electrical measurements. (C) Optical microscope image of an actual device (the white bar in the right bottom corner is 200 μm long). In fact, two separate graphene flakes are visible on the substrate, but only one of them is immersed in the ionic liquid. Also clearly visible are the two Pt wires immersed in the ionic liquid, acting as gate and quasi-reference electrodes.