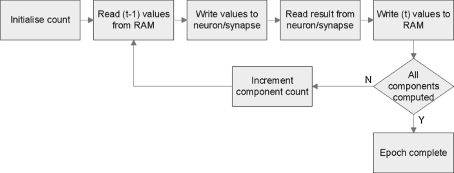

Fig. 4.

A flow diagram of the time division multiplexing scheme. With time step 1 ms, each loop could be 1000 iterations when FPGA running at 100 MHz. Each neuron processing units read neuron data and synapses weights from off-chip RAM and accumulated membrane potential according to current time step value on each iteration. The calculated values are stored in off-chip RAM after one epoch completes