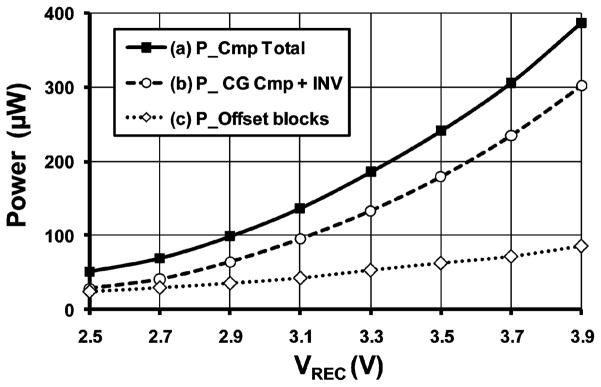

Fig. 9.

Simulated power consumption of the comparator versus VREC showing power overheads for employing the offset-control functions (fc = 13.56 MHz, RL = 500 Ω, and CL = 10 μF). Curve (a) shows the total power consumption of the high speed comparator, (b) is the power consumption of the CG comparator and CS inverters, and (c) indicates the consumption of the offset-control blocks.