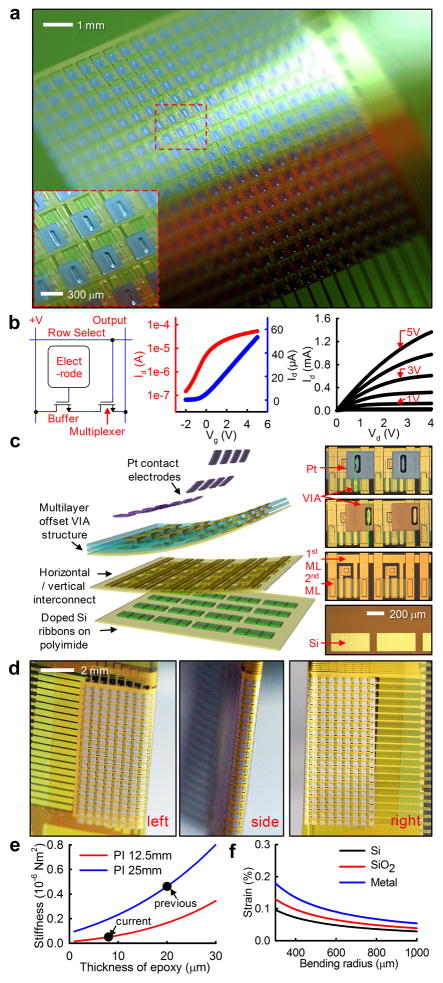

Figure 1. Flexible, high-resolution multiplexed electrode array.

a, Photograph of a 360 channel high density active electrode array. The electrode size and spacing was 300 μm × 300 μm and 500 μm, respectively. (inset) A closer view showing a few unit-cells. b, Schematic circuit diagram of single unit-cell containing two matched transistors (left), transfer characteristics of drain-to-source current (Ids) from a representative flexible transistor on linear (blue) and logarithmic (red) scales as gate to source voltage (Vgs) was swept from −2 to +5 V, demonstrating the threshold voltage (Vt) of the transistor (center). Current-voltage characteristics of a representative flexible silicon transistor (right). Ids was plotted as a function of drain-to-source voltage (Vds). Vgs was varied from 0 to 5 V in 1–V steps. c, Schematic exploded view (left) and corresponding microscope image of each layer: doped silicon nanoribbons (right frame, bottom), after vertical and horizontal interconnection with arrows indicating the 1st and 2nd metal layers (ML) (right frame, 2nd from bottom), after water-proof encapsulation (right frame, 3rd from bottom) and after platinum electrode deposition (right frame, top). Green dashed lines illustrated the offset via structure, critical to preventing leakage current while submerged in conductive fluid. d, Images of folded electrode array around low modulus Polydimethylsiloxane (PDMS) insert. e, bending stiffness of electrode array for varying epoxy thicknesses and two different PI substrate thicknesses. A nearly 10-fold increase in flexibility between the current device and our prior work was shown. f, Induced strain in different layers depending on the change in bending radius.