# NIH Public Access

**Author Manuscript**

*Nano Lett.* Author manuscript; available in PMC 2012 June 8

Published in final edited form as:

Nano Lett. 2011 June 8; 11(6): 2555–2559. doi:10.1021/nl201331x.

# **Top-gated CVD Graphene Transistors with Current Saturation**

Jingwei Bai<sup>†</sup>, Lei Liao<sup>‡</sup>, Hailong Zhou<sup>‡</sup>, Rui Cheng<sup>†</sup>, Lixin Liu<sup>‡</sup>, Yu Huang<sup>†,&,\*</sup>, and Xiangfeng Duan<sup>‡,&,\*</sup>

<sup>†</sup>Department of Materials Science and Engineering, University of California, Los Angeles, CA 90095

<sup>‡</sup>Department of Chemistry and Biochemistry, University of California, Los Angeles, CA 90095

<sup>&</sup>California Nanosystems Institute, University of California, Los Angeles, CA 90095

## Abstract

Graphene transistors are of considerable interest for radio frequency (RF) applications. In general, transistors with large transconductance and drain current saturation is desirable for RF performance, which is however nontrivial to achieve in graphene transistors. Here we report high performance top-gated graphene transistors based on chemical vapor deposition (CVD) grown graphene with large transconductance and drain current saturation. The graphene transistors were fabricated with evaporated high dielectric constant material (HfO<sub>2</sub>) as the top-gate dielectrics. Length scaling studies of the transistors with channel length from 5.6  $\mu$ m to 100 nm shows that complete current saturation can be achieved in 5.6  $\mu$ m devices and the saturation characteristics degrade as the channel length shrinks down to 100–300 nm regime. The drain current saturation was primarily attributed to drain bias induced shift of the Dirac points. With the selective deposition of HfO<sub>2</sub> gate dielectrics, we have further demonstrated a simple scheme to realize a 300 nm channel length graphene transistors with self-aligned source-drain electrodes to achieve the highest transconductance of 250  $\mu$ S/ $\mu$ m reported in CVD graphene to date.

### Keywords

Graphene; transistors; dielectrics; current saturation; self-alignment

Graphene exhibits many unique characteristics, including the highest carrier mobility, the highest carrier saturation velocity and highest thermal conductivity, that make it an attractive electronic material for ultra high-speed radio frequency applications.<sup>1–7</sup> In particular, graphene transistors with maximum cut-off frequency exceeding 100 GHz have been recently demonstrated using epitaxial graphene or CVD grown graphene.<sup>6–7</sup> This exceptional performance advancement is achieved by continued shrinking the transistor channel length. However, the performance of these devices is still at least partly limited by the presence of access resistance due to the gaps exist between the source-gate and gate-drain electrodes. In the state-of-art silicon metal-oxide-semiconductor field-effect transistor (MOSFET) technology, a self-aligned gate structure is used to ensure the precise positioning of source, drain and gate electrode to reduce the gaps and overlaps between gate and source or drain in order to simultaneously minimize the access resistance and parasitic capacitance for desired transistor performance. However, the traditional fabrication processes in silicon MOSFET technology cannot be readily applied to graphene transistors due to the difficulties

<sup>\*</sup>To whom correspondence should be addressed. xduan@chem.ucla.edu, yhuang@seas.ucla.edu.

Supporting Information: Additional description of graphene growth method, characterization of evaporated HfO<sub>2</sub>, and plot of saturation conductance.

associated with selective deposition and pattern of dielectric materials on graphene without degrading the structure or electronic performance of graphene. A self-aligned process has recently been developed using synthetic metal/dielectric core/shell nanowires as the gate, and enabled graphene transistors with cut-off frequency reaching 300 GHz or higher.<sup>4,8</sup> The scalable fabrication of graphene transistors using this approach, however, is complicated with the usage of the mechanically peeled graphene flakes and the requirement of unconventional nanowire assembly process. It therefore remains a significant challenge to realize short channel transistors for high frequency applications due to the difficulties in selective patterning the dielectric layer on grapheme in large scale. Additionally, the transistors reported in these previous efforts showed little drain current saturation, which is undesirable for power gain performance.<sup>9</sup> Although drain current saturation has been reported in phonon scatter limited velocity saturation regime using exfoliated graphene or with h-BN as the back gate dielectrics,<sup>10–13</sup> it has not been reported in CVD graphene to date.

To address these challenges, here we report our effort in exploring an evaporation process that can allow for selective deposition of a high-dielectric constant (high-*k*) dielectric layer on large area CVD graphene enabling the self-aligned fabrication of graphene transistors. Importantly, high performance top-gated CVD graphene transistors have been fabricated with clear drain current saturation. Self-aligned graphene transistor is fabricated with a record high transconductance of 250  $\mu$ S/ $\mu$ m obtained in CVD graphene device. Using a conventional lithography and CVD grown graphene, this process opens opportunity for the large scale fabrication of high performance graphene transistors.

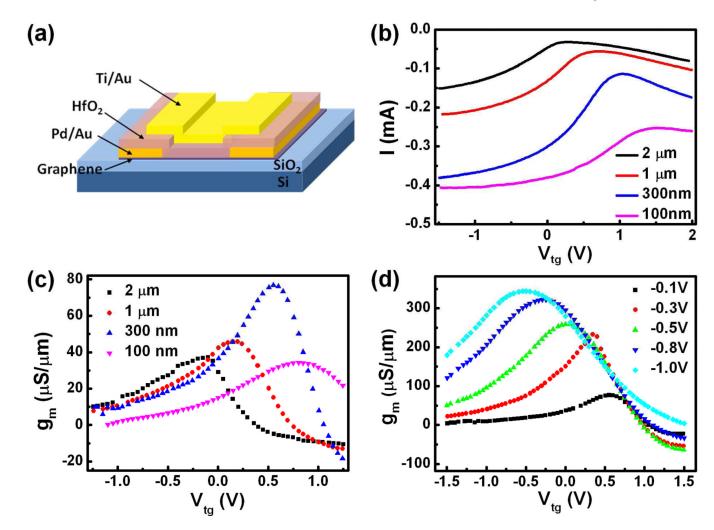

The graphene transistors studied here consist of CVD grown graphene as the channel material, Pd/Au thin film as the source and drain electrodes, and HfO<sub>2</sub>/Ti/Au as the top gate stack (Fig. 1). To make the device, high quality single layer graphene was grown on Cu foil based on an ambient pressure CVD method (supplementary materials) and transferred onto silicon substrate (with 300 nm SiO<sub>2</sub> on top).<sup>14,15</sup> The graphene was then patterned into strips with desired width through a photolithography and oxygen plasma etching process. The source-drain electrodes were next defined by e-beam lithography followed by e-beam evaporation deposition of Pd/Au (10/30 nm) thin film. After forming the contact electrodes, a 40 nm HfO<sub>2</sub> film was evaporated onto the graphene substrate as the top gate dielectrics by e-beam evaporation.<sup>16</sup> The dielectric constant of evaporated HfO<sub>2</sub> thin film was measured to be ~ 19 (Fig. S2), comparable to the reported values for e-beam evaporated HfO<sub>2</sub>.<sup>17-19</sup> The top-gate electrode was subsequently formed by e-beam lithography patterning and metallization process (Ti/Au). Devices with different channel length (L) were fabricated to study the channel length scaling behavior. To investigate the basic device performance, the grapheme transistors were fabricated with complete gate to source or drain overlapping to minimize the access resistance.

Figure 1b depicts the representative transfer characteristics with channel length ranging from 2  $\mu$ m to 100 nm. The devices show typical characteristics of p-type doping and electron-hole asymmetry in which the Dirac points are located at positive gate voltage with a suppression of electron conduction branch. The p-type doping is attributed to oxygen doping during graphene growth and transfer process, and the electron-hole asymmetry is likely originated from imbalanced carrier injection caused by misalignment between the contact electrode work function and channel neutrality points.<sup>20</sup> The hole transport branches switch from saturation to current minimum in a gate voltage span of about 2 V. A general trend of positive shift of Dirac point and decrease of on-off ratio is observed with the decrease of channel length. This can be explained as a short channel effect: in short channel device, where the channel potential is strongly affected by the drain potential, a more opposite voltages is needed to turn off the channel.<sup>21</sup> Similar to the silicon p-MOSFETs short channel

Nano Lett. Author manuscript; available in PMC 2012 June 8.

threshold roll-off, in graphene FETs when current carriers are holes, a more positive voltage is needed to reach the current minimum, leading to a positive shift of Dirac point with down scaling of the channel length. On the other hand, the transconductance in shorter channel device increases due to the reduction of channel resistance. The peak transconductance at bias of 100 mV increases from  $36 \,\mu\text{S}/\mu\text{m}$  (L=2  $\mu\text{m}$ ) to  $77 \,\mu\text{S}/\mu\text{m}$  (L=300 nm) (Fig. 1c). However, a further shrinkage of channel length to 100 nm results in a reduction of peak transconductance to  $34 \,\mu\text{S}/\mu\text{m}$ , due to a short channel effect.<sup>21</sup> The transconductance is also highly dependent on the drain voltage. The measured largest transconductance is  $350 \,\mu\text{S}/\mu\text{m}$  obtained at L=300 nm and V<sub>ds</sub> of  $-1 \,\text{V}$  (Fig. 1d).

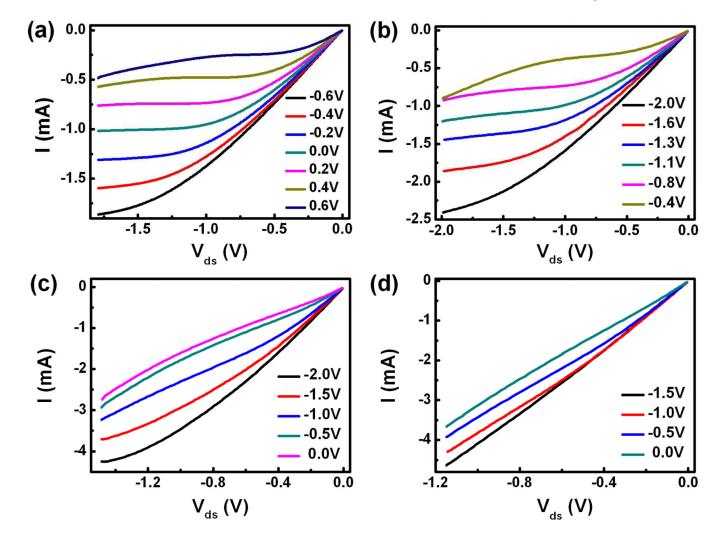

Interestingly, our fabricated graphene transistors show clear drain current saturation at relative low voltage (-1 V to -1.4 V) (Fig. 2). A full current saturation is achieved in a long channel device (L=5.6  $\mu$ m), exhibiting near zero drain source conductance (g<sub>ds</sub>) (< 2  $\mu$ S/ $\mu$ m) in the saturation region (Fig. 3a, S3). The  $g_{ds}$  is about 47  $\mu$ S/ $\mu$ m for L=2  $\mu$ m device and 65  $\mu$ S/ $\mu$ m for L=300 nm channel device (V<sub>ds</sub>=1.4 V and V<sub>g</sub>=-2 V). Little saturation is found when L shrinks down to 100 nm. A important figure-of-merit in analog amplifiers is evaluated by intrinsic gain  $(g_m/g_{ds})$  which represents the theoretical maximum gain achievable by a single transistor.<sup>9</sup> Previously reported graphene RF devices show little drain saturation with a relatively large drain conductance and low intrinsic gain typically smaller than unit, making it less interesting for practical amplifier applications. In our case, the intrinsic gain for L=5.6  $\mu$ m device is estimated to be larger than 50 (at V<sub>ds</sub>=-1.3 V, V<sub>o</sub>=0.2 V). This value drops to 7 for L=2 µm and to about 4 for L=300 nm devices. Although similar current saturation was previously reported in graphene devices made by high quality exfoliated graphene,<sup>10–13</sup> our work demonstrated for the first time that current saturation can also been achieved in devices produced on CVD grown graphene, making it possible for large scale fabrication of graphene devices with desirable intrinsic gain.

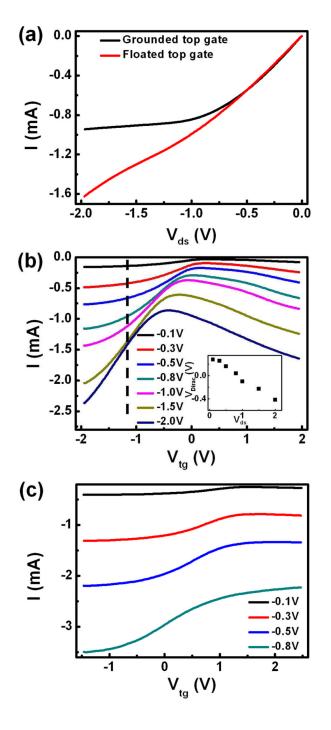

To further probe the origin of the saturation behavior in our graphene transistors, we focus on a device showing good p-type doping and saturation characteristics at zero gate (gate grounded at zero bias) (black curve in Fig. 3a). Interestingly, no clear current saturation is observed in the same device when the gate electrode is floated, suggesting that the current saturation observed here is likely due to the relative potential between the drain and gate (ie: bias induced additional gating effect), rather than the intrinsic velocity saturation associated with phonon scattering. In field-effect transistors, bias voltage alters the channel potential in a way equivalent to a gate voltage with opposite sign coupled through the oxide. In analogy to the pinch-off behavior in silicon device, a negative bias in graphene transistor creates a relative positive potential in the gate (in reference to the drain) to deplete the holes at the drain end, and current saturation is observed when the minimal carrier density is reached. Usually, a good gate coupling (large Cox) is needed in order to achieve saturation at relative low bias voltage, which we can achieve with the evaporated high-k dielectrics. The pinch-off effect has also been evaluated in exfoliated graphene FETs by Meric et. al., where the observed current saturation was attributed to phonon scattering induced velocity saturation.<sup>10</sup> Additionally, the  $g_{ds}$  rise up with further increase  $V_{ds}$  beyond the saturation voltage, produce a current kink in the I– $V_{ds}$  curve.<sup>22-24</sup> It can be explained by the formation of additional electron conduction channel at the drain end as the pinch-off point moves into the channel. The current kink is a unique characteristic for ambipolar transistors. Similar results were also found in carbon nanotube ambipolar transistors.<sup>22–24</sup>

The drain bias induced gating effect can be better viewed by observing the shift of Dirac point with different drain bias voltages. As shown in a family  $I-V_g$  curves with different drain bias  $V_{ds}$  (Fig. 3b), the increase of negative  $V_{ds}$  not only increases the overall current, but also shifts the curves to negative voltage direction. In conjunction with the sharp switching of hole transport branch, the  $I-V_{tg}$  curves at different bias voltage grow closer to

Nano Lett. Author manuscript; available in PMC 2012 June 8.

each other with the increase of negative  $V_{ds}$  so that the drain current saturation can be reached (for example, along the dash line in Fig. 3b). In ambipolar transistors, a current minimum point is reached when electron/hole current injected from source/drain is balanced with each other, in equivalent to hold the Dirac point at zero gate voltage and apply equal and opposite voltage  $(\pm 1/2V_{ds})$  to source and drain. Therefore, the gate-source or gate-drain potential difference, which is also the Dirac point voltage when either the source or drain are grounded, will shift by  $1/2\Delta V_{ds}$  with a change of bias voltage  $\Delta V_{ds}$ . In our long channel device, the Dirac point shifts approximately -0.7 V when  $V_{ds}$  increase from -0.1 V to -2 V (Fig. 3b and inset), close to the theoretical prediction. Similar effect was reported in ambipolar graphene or carbon nanotube FETs.<sup>21,22–24</sup> On the other hand, when channel length shrinks down to 100 nm, the short channel effect starts to dominate. As discussed above, the short channel effect will move the Dirac point to the opposite side of applied bias, leading to a positive shift of Dirac point with a negative  $V_{ds}$ . As a result, the Dirac point shifts to positive voltage at L=100 nm and no current saturation is observed (Fig. 3c, 2d). This also explains the observation of weak saturation at L=300 nm.

Selective deposition of HfO<sub>2</sub> dielectric layer on CVD graphene can allow for the fabrication of the self-aligned graphene devices (Fig. 4a). To fabricate the device, a narrow strip of the gate stack (HfO<sub>2</sub>/Cr/Au: 40 nm/4 nm/20 nm) is first defined on graphene by one step e-beam lithography followed by vacuum deposition and lift-off processes. After the formation of the gate stack, a thin layer of Pt (10 nm) is deposited on top of graphene and across the pre-formed gate stack, in which the gate stack separate the Pt thin film into two separated pads as the self-aligned source and drain electrodes (Fig. 4a). The transport measurement shows only slight saturation in the output characteristics (Fig. 4d), likely due to the short channel effect. The transfer characteristics are similar to devices described above. The device shows an on-off ratio of 2 within a full on-off swing in the gate range of 0–1.5 V. The self-aligned structure can enable small access resistance to ensure a large delivery current up to 0.44 mA/ $\mu$ m at V<sub>ds</sub>=-0.8 V and V<sub>g</sub>=0.8 V. The transconductance reaches 250 µS/µm at V<sub>ds</sub>=-0.5 V, and degrades with further increase in bias voltage. To the best of our knowledge, the scaled on-current and transconductance obtained here represents the highest value among the reported CVD graphene transistors.

In conclusion, we have shown that high performance transistor can be obtained by using the CVD graphene as the channel and the evaporated  $HfO_2$  as the gate dielectrics. A drain current saturation can be achieved in graphene transistors with channel length down to 300 nm, which was attributed to the bias induced shift of the Dirac point. We have also demonstrated a simple scheme to realize a self-aligned gate structure with the best transconductance reported for CVD graphene transistor to date. Combining with the development of large area CVD graphene, this simple lithography based self-alignment method could open up exciting opportunities for large scale fabrication of high performance graphene devices.<sup>25</sup>

# **Supplementary Material**

Refer to Web version on PubMed Central for supplementary material.

#### Acknowledgments

Y.H. acknowledges support by the NIH Director's New Innovator Award Program, part of the NIH Roadmap for Medical Research, through grant number 1DP2OD007279. X.D. acknowledges support by NSF CAREER award 0956171.

#### References

- 1. Jeon DY, Lee KJ, Kim M, Kim DC, Chung HJ, Woo YS, Seo S. Jap. J. Appl. Phys. 2009; 48:091601.

- Lin YM, Jenkins KA, Valdes-Garcia A, Small JP, Farmer DB, Avouris P. Nano Lett. 2009; 9:422– 426. [PubMed: 19099364]

- Moon JS, Curtis D, Hu M, Wong D, McGuire C, Campbell PM, Jernigan G, Tedesco JL, VanMil B, Mvers-Ward R, Eddy CJ, Gaskil DK. IEEE Electron. Device Lett. 2009; 30:650–652.

- Liao L, Lin YC, Bao MQ, Cheng R, Bai JW, Liu YA, Qu YQ, Wang KL, Huang Y, Duan XF. Nature. 2010; 467:305–308. [PubMed: 20811365]

- 5. Lin YM, Chiu HY, Jenkins KA, Farmer DB, Avouris P, Valdes-Garcia A. IEEE Electron. Device Lett. 2010; 31:69–70.

- Lin YM, Dimitrakopoulos C, Jenkins KA, Farmer DB, Chiu HY, Grill A, Avouris P. Science. 2010; 327:662–662. [PubMed: 20133565]

- Wu YQ, Lin YM, Bol AA, Jenkins KA, Xia FN, Farmer DB, Zhu Y, Avouris P. Nature. 2011; 472:74–78. [PubMed: 21475197]

- Liao L, Bai JW, Cheng R, Lin YC, Jiang S, Qu YQ, Huang Y, Duan XF. Nano Lett. 2010; 10:3952– 3956. [PubMed: 20815334]

- 9. Schwierz F. Nature Nanotechnol. 2010; 5:487-496. [PubMed: 20512128]

- Meric I, Han MY, Young AF, Ozyilmaz B, Kim P, Shepard KL. Nature Nanotechnol. 2008; 3:654–659. [PubMed: 18989330]

- Barreiro A, Lazzeri M, Moser J, Mauri F, Bachtold A. Phys. Rev. Lett. 2009; 103:076601. [PubMed: 19792670]

- Freitag M, Steiner M, Martin Y, Perebeinos V, Chen ZH, Tsang JC, Avouris P. Nano Lett. 2009; 9:1883–1888. [PubMed: 19331421]

- 13. Meric I, Dean CR, Young AF, Hone J, Kim P, Shepard KL. arXiv:1101.4712. 2011

- Li XS, Zhu YW, Cai WW, Borysiak M, Han BY, Chen D, Piner RD, Colombo L, Ruoff RS. Nano Lett. 2009; 9:4359–4363. [PubMed: 19845330]

- Bhaviripudi S, Jia XT, Dresselhaus MS, Kong J. Nano Lett. 2010; 10:4128–4133. [PubMed: 20812667]

- Kedzierski J, Hsu PL, Reina A, Kong J, Healey P, Wyatt P, Keast C. IEEE Electron. Device Lett. 2009; 30:745–747.

- 17. Cherkaoui K, Monaghan S, Negara MA, Modreanu M, Hurley PK, O'Connell D, McDonnell S, Hughes G, Wright S, Barklie RC, Bailey P, Noakes TCQ. J. Appl. Phys. 2008; 104:064113.

- Harris H, Choi K, Mehta N, Chandolu A, Biswas N, Kipshidze G, Nikishin S, Gangopadhyay S, Temkin H. Appl. Phys. Lett. 2002; 81:1065–1067.

- 19. Zhu J, Li YR, Liu ZG. J. Phy. D-Appl. Phys. 2004; 37:2896-2900.

- Farmer DB, Golizadeh-Mojarad R, Perebeinos V, Lin YM, Tulevski GS, Tsang JC, Avouris P. Nano Lett. 2009; 9:388–392. [PubMed: 19102701]

- 21. Han SJ, Sun YN, Bol AA, Haensch W, Chen ZH. VLSI Technical Digest. 2010:231-232.

- 22. Chen YF, Fuhrer MS. Phys. Rev. Lett. 2005; 95:236803. [PubMed: 16384328]

- 23. Misewich JA, Martel R, Avouris P, Tsang JC, Heinze S, Tersoff J. Science. 2003; 300:783–786. [PubMed: 12730598]

- 24. Radosavljevic M, Heinze S, Tersoff J, Avouris P. Appl. Phys. Lett. 2003; 83:2435-2437.

- Bae S, Kim H, Lee Y, Xu XF, Park JS, Zheng Y, Balakrishnan J, Lei T, Kim HR, Song YI, Kim YJ, Kim KS, Ozyilmaz B, Ahn JH, Hong BH, Iijima S. Nature Nanotechnol. 2010; 5:574–578. [PubMed: 20562870]

Page 5

Bai et al.

#### Figure 1.

(a) Schematic illustration of the device structure of top gated graphene transistors for the evaluation of the channel length scaling effect. (b) Transfer characteristics of top-gated graphene transistor at  $V_{ds}$ =-0.1V with channel lengths 2 µm, 1 µm, 300 nm and 100 nm. The channel width is 3.4 µm for all devices. (c) The corresponding transconductance of the devices shown in (b) at  $V_{ds}$ =-0.1V. (d) The evolution of transconductance with gate voltage for the 300 nm channel device at bias voltage -0.1V, -0.3V, -0.5V, -0.8V and -1.0V.

Bai et al.

Figure 2.

Output characteristics showing the current saturation behavior for devices with variable channel lengths: (a) L=5.6  $\mu$ m, (b) 2  $\mu$ m, (c) 300 nm, and (d) 100 nm.

Nano Lett. Author manuscript; available in PMC 2012 June 8.

Bai et al.

#### Figure 3.

(a) I–V characteristic of a long channel device (L=5.6  $\mu$ m) under grounded or floated gate condition. (b) Transfer characteristic at different bias voltage for the device with L=2  $\mu$ m. The inset shows Dirac point shift as a function of bias voltage. (c) Transfer characteristic at different bias voltage for the device with L=100 nm.

Bai et al.

#### Figure 4.

(a) Schematic (top), top view (bottom left) and cross section (bottom right) SEM image of a typical self-aligned device. The scale bar indicates 2  $\mu$ m in the top view SEM image, and 200nm in the cross section SEM image. (b) Transfer characteristic and (c) corresponding transconductance under different bias voltage for an L=300 nm self-aligned device. (d) Output characteristics of the same device.