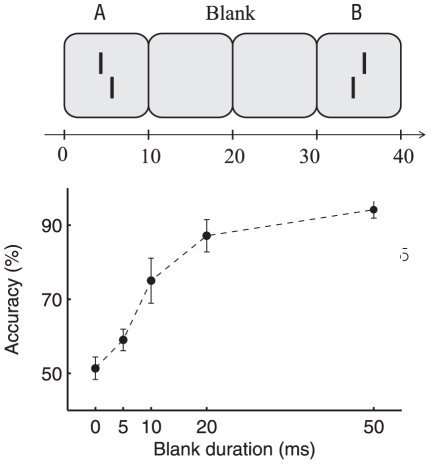

Figure 1. Reference Experiment.

Upper panel: A left or right offset vernier was presented for 10 ms followed by a variable blank background (ISI, here shown for 20 ms) and, then, by a second vernier for 10 ms. Lower panel: Observers were asked to indicate whether the first or second vernier was offset to the right. Performance improves quickly with increasing ISI, reaching ceiling performance at 50 ms.