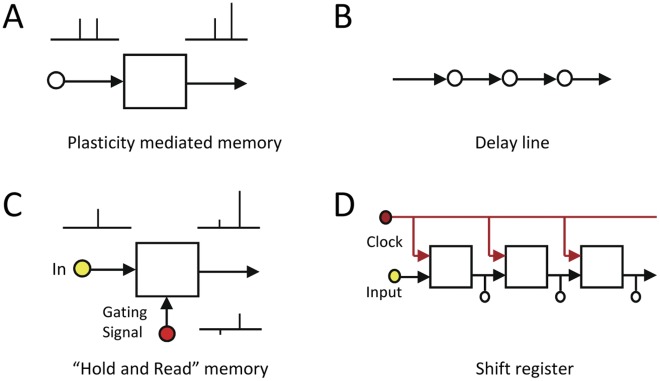

Figure 1. Feedforward memory architecture and it building blocks.

(A) Plasticity mediated memory mechanisms such as paired pulse facilitation is better suited for feedback rather than feedforward memory, because they require repeating inputs. (B) The delay line is the simplest scheme for a feedforward memory network. Each element accepts the value of its upstream neighbor and transfers its current value to its downstream neighbor. When repeated iteratively the network transforms a time sequence into a spatial sequence. It is a memory mechanism because the spatial sequence accurately holds information on events that occurred in the past. (C) Crucial requirements for the building block of an effective feedforward memory are that each element be able to hold an input signal for a substantial length of time, and that the signal can then be read out without the signal being repeated. “Dendritic Hold and Read” (DHR), described here, can implement these requirements on individual dendrites. (D) The ‘shift register’ is the digital implementation of the delay line. It is used as the memory buffer at the input stage of the central processor unit (CPU) in digital computers. In this case the individual information holding element is the binary flipflop. It is a discrete time network because information is binary and is moved forward at set time intervals by a clock. The entire spatial sequence can be accessed by tapping the output of each of the flipflops simultaneously.