# A practical guide for the fabrication of microfluidic devices using glass and silicon

Ciprian Iliescu, <sup>1,a)</sup> Hayden Taylor, <sup>2,3,a)</sup> Marioara Avram, <sup>4</sup> Jianmin Miao, <sup>2</sup> and Sami Franssila<sup>5</sup>

<sup>1</sup>Institute of Bioengineering and Nanotechnology, 31 Biopolis Way, The Nanos #04-01, 138669, Singapore

<sup>2</sup>School of Mechanical and Aerospace Engineering, Nanyang Technological University, 50 Nanyang Avenue, 639798, Singapore

<sup>3</sup>Singapore–MIT Alliance for Research and Technology, 3 Science Drive 2, 117543, Singapore

<sup>4</sup>National Institute for Research and Development in Microtechnologies, Bucharest, Romania

<sup>5</sup>Department of Materials Science and Engineering, School of Science and Technology, Aalto University, FI-00076 Aalto, Finland

(Received 26 November 2011; accepted 8 February 2012; published online 5 March 2012)

This paper describes the main protocols that are used for fabricating microfluidic devices from glass and silicon. Methods for micropatterning glass and silicon are surveyed, and their limitations are discussed. Bonding methods that can be used for joining these materials are summarized and key process parameters are indicated. The paper also outlines techniques for forming electrical connections between microfluidic devices and external circuits. A framework is proposed for the synthesis of a complete glass/silicon device fabrication flow. © 2012 American Institute of Physics. [http://dx.doi.org/10.1063/1.3689939]

### I. WHY USE SILICON AND GLASS IN MICRO- AND NANO-FLUIDIC APPLICATIONS?

Micro- and nano-fluidic technology continues to be embraced by biologists, <sup>1-3</sup> chemists, <sup>4</sup> and engineers throughout academia and industry. As its applications have expanded, there has been an explosion in the range of materials and processes used to fabricate these devices. The earliest microfluidic devices (e.g., gas<sup>5</sup> and liquid<sup>6</sup> chromatography devices) were made from silicon and glass and borrowed processes directly from semiconductor and microelectromechanical systems (MEMS) manufacturing. <sup>7</sup> Now, however, many researchers have moved away from silicon and glass, and instead use cast elastomers such as polydimethylsiloxane (PDMS)—which is ideal for swift prototyping—or thermoplastic polymers, which can be hot-embossed or injection-molded and are well suited to inexpensive manufacturing. Yet, there remain many applications where glass and silicon offer advantages over polymeric materials. In this paper, we highlight these advantages and offer a framework for selecting fabrication processes when using silicon and glass.

# A. The dominance of soft lithography

Over the last decade, PDMS has become virtually the default material for forming microfluidic devices, because of the sheer ease with which it can be cast on to a micro-scale mould and then strongly bonded to glass. The elastomeric nature of the material has been exploited to integrate fluidic valves and pumps on-chip and has simplified the production of multi-layer devices because the soft layers readily conform to each other. 10,11 Yet, the low stiffness (usually <1 MPa) of PDMS relative to amorphous thermoplastics, silicon, and glass has its own

<sup>&</sup>lt;sup>a)</sup>Authors to whom correspondence should be addressed. Electronic addresses: ciliescu@ibn.a-star.edu.sg and hkt@ntu.edu.sg.

drawbacks. High aspect-ratio channels are notoriously difficult to fabricate in PDMS because of their propensity to collapse. <sup>12</sup> Moreover, difficulties in automating the handling of such a soft material have hampered efforts to scale up PDMS device manufacturing. Meanwhile, PDMS's high oxygen and water permeabilities have proved both a blessing and a curse in different applications.

The hydrophobic nature of PDMS can be an important consideration for some biological applications. In drug screening applications, for example, hydrophobic drugs as well as metabolites (urea or albumin) can be absorbed into the device's material due to hydrophobic—hydrophobic interactions. Moreover, the limited repeatability of the PDMS fabrication process remains a big challenge that makes the material more suitable for research labs than for industrial applications. <sup>13</sup>

Alternative elastomers for microfluidics include off-stoichiometric thiol-ene (OSTE)<sup>14</sup> and thermoplastic elastomers.<sup>15</sup> Compared with PDMS, these materials allow a wider range of property tailoring (e.g., stiffness and permeability) and potentially faster processing.

# B. Exploration of alternative polymeric materials

Attention has turned in recent years to harder, less permeable, and amorphous thermoplastic polymers that can be micro-embossed or injection-moulded—such as polymethylmethacry-late (PMMA), polycarbonate, and cyclic olefin (co)polymers. <sup>16</sup> Injection moulding tooling costs are high—\$20k-30k is typical—and, therefore, short production runs are expensive, even compared to silicon and glass processing. For hot micro-embossing, meanwhile, cheaper masters can be used, but the cycle time of embossing is slower: often 5–10 min vs. 5–10 s for injection moulding.

Amorphous polymers can form features with higher depth-to-width aspect ratios than are possible with PDMS. Moreover, because of the higher stiffness of thermoplastics, channels of a given aspect ratio are more collapse-resistant than those made from PDMS. Thermoplastics, however, do not lend themselves as well as PDMS to making multi-layer devices or to the integration of valves and membranes. The robust integration of electrodes with both PDMS and thermoplastic devices remains a challenge: metal films deposited on flexible substrates are highly susceptible to fracture. Although thermoplastic fabrication technologies are very promising, the production of devices using these materials is still at an early stage of development.

The negative-tone epoxy photoresist SU-8 has also been widely used in microfluidics. SU-8 is simple to pattern by photolithography, <sup>17</sup> can readily be bonded to itself, <sup>18</sup> and offers a reasonable combination of mechanical strength and chemical tolerance. For example, the mechanical properties of SU-8 have been exploited to make check valves. <sup>19</sup> Its surface properties have been exploited to make capillary electrophoresis chips. <sup>20</sup> Its ease of precise patterning has enabled the fabrication of electrospray tips. <sup>21</sup> Its good thermal stability and compatibility with electrode integration have enabled its use in polymerase chain reactors. <sup>22</sup>

More recently, paper and woven fabrics have emerged as inexpensive substrate materials for simple fluidic devices.<sup>23</sup> Sub-millimeter channel structures can be defined on paper by the printing of hydrophobic (e.g., wax) patterns.

## C. The remaining advantages of silicon and glass

Certain micro- and nano-fluidic applications demand high temperature resilience (e.g., for chemical synthesis<sup>4</sup>), the precise definition of nano-scale channels or pores, <sup>24,25</sup> high aspect ratio structures (usually up to 20:1), the integration of electrodes, or even integration with electronic circuits. In these cases, the higher costs of materials, energy, and capital equipment involved in silicon or glass processing may be warranted.

In some applications, the high thermal conductivity of silicon is of use in ensuring a uniform temperature distribution.<sup>26</sup> In contrast, when thermally insulating substrates like glass are used, large temperature gradients can be generated. One special benefit of silicon is the ability to fabricate thin membranes, which reduce thermal mass and enable high temperature ramp-rates.<sup>27</sup> Meanwhile, the mechanical properties of silicon have been exploited to fabricate pumps<sup>28</sup> and valves,<sup>29</sup> and in

making complex 3D structures, for example nebulizer chips,<sup>30</sup> microreactors,<sup>27</sup> cell growth chambers,<sup>31</sup> and electrospray tips.<sup>32</sup> Glass has been used in applications ranging from capillary electrophoresis<sup>33</sup> to polymerase chain reactions (PCR)<sup>34</sup> and to gas chromatographs.<sup>35</sup>

Hybrid silicon–glass, silicon–polymer, or glass–polymer devices can be made, but the differences in material properties need to be understood. For example, in a comparison of capillary electrophoresis chips made of single materials vs. bonded dissimilar materials, the single-material devices performed better.<sup>36</sup>

In this article, we detail the advantages offered by glass and silicon and suggest a framework for selecting fabrication processes. We also describe key considerations for designing a glass and/or silicon process flow.

## **II. DEVICE DESIGN APPROACHES**

In fabricating a glass and/or silicon device, three basic approaches can be taken: *surface micromachining*, *buried-channel* techniques, and *bulk micromachining*.

In surface micromachining, a sacrificial layer is patterned to define the desired fluidic channels, a structural layer is deposited, and the sacrificial layer is then etched away. Surface micromachining offers greater potential for making multi-layer devices than does bulk micromachining, but involves more process steps per layer. A number of promising surface-micromachined microfluidic devices have been reported (e.g., Refs. 37 and 38). Surface micromachining is particularly attractive for the fabrication of nano-channels<sup>39</sup> because the thickness of the sacrificial layer, and hence the final channel height, can generally be controlled during deposition or growth within a few nanometres. Bulk micromachining cannot offer such precise control of channel height because of spatial etch-rate variations.

In buried-channel technology, a deep, vertical access trench is etched into silicon by anisotropic deep reactive ion etching (DRIE), its sidewalls are passivated by chemical vapour deposition (CVD), and a circular channel is then etched isotropically, centred on the bottom of the access trench. This technology works best when very deep, narrow access features are used, necessitating micron-scale lithography and high aspect-ratio DRIE. More recently, a variant of the technique has emerged in which isotropic DRIE is used to etch bulk silicon beneath a perforated silicon nitride mask, and CVD then seals the access holes in the mask. Unlike traditional surface micromachining, the silicon bulk itself is used as a sort of sacrificial layer and the channel height can be many micrometers. The mechanical stability of the thin-film roof is a limitation in some applications.

The most prevalent fabrication approach, however, is bulk micromachining, in which micro- and nano-fluidic channels are formed by removing material from a wafer and bonding or adhering it to another wafer to encapsulate the channels. In the rest of this paper, we focus on bulk micromachining.

# **III. PROCESS SELECTION**

In this section, we address the selection of patterning, bonding, and electrode integration processes in turn. A process-selection framework is presented in Table I.

In choosing a patterning method, the capabilities of candidate processes need to be evaluated against target feature dimensions, their tolerances, and any limitations on surface roughness. Quinn *et al.* propose a systematic approach to choosing micropatterning processes for MEMS, <sup>43</sup> which could be valuable for designing micro- and nano-fluidic process flows. Here, we discuss in detail the capabilities of wet and dry etching of bulk glass and silicon.

All of the etching processes that we describe require the etched material to be *masked* with an etch-resistant layer. The mask must be patterned to expose those regions of the underlying material that are to be etched. As we explain below, the mask might be a metallic, ceramic, or polymeric layer, or a multi-layer combination of these material types. To pattern the mask layer, it is usual to apply a photoresist layer and expose it by photolithography before chemically developing the photoresist and etching the mask. The narrowest feature size that can be patterned using photolithography is limited by diffraction to around  $0.5~\mu m$  for contact

TABLE I. Selection of the fabrication process according to the requirements of the application (optical, geometrical, electrical, and thermal).

|      |                                                                  |                                            |                                                              | Possible processing routes and criteria for their sele                                                                                                                                                                                                                                                                                     | ion (preferred process options are shown in bold)                                                                                                                                                                                                                                              |  |

|------|------------------------------------------------------------------|--------------------------------------------|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Step | Selection to be made                                             |                                            |                                                              | Route A                                                                                                                                                                                                                                                                                                                                    | Route B                                                                                                                                                                                                                                                                                        |  |

| 1    | Materials involved i                                             | s involved in the microfabrication process |                                                              | • Glass/glass (take this route if the application requires optical transparency of the device)                                                                                                                                                                                                                                             | • Glass/silicon (a more common and well established route)                                                                                                                                                                                                                                     |  |

| 2    | Patterning method Microchannels  Through-holes for fluidic ports |                                            |                                                              | Wet etching in HF/HCl     Dry etching (recommended only if vertical walls or high aspect ratio structures are required)                                                                                                                                                                                                                    | Dry etching of the silicon     For complex microfluidic devices requiring multiple channel layers, the silicon wafer can be patterned on both sides and via holes etched through the wafer to connect them; alternatively, the glass can be patterned (by wet etching) as well as the silicon. |  |

|      |                                                                  |                                            | fluidic ports                                                | Wet etching     Sand-blasting     Drilling                                                                                                                                                                                                                                                                                                 | Dry etching     Laser-drilling     Sand-blasting                                                                                                                                                                                                                                               |  |

| 3    | Bonding method                                                   | No electrical connection                   | The device operates above $\sim 200^{\circ}\mathrm{C}$       | • Fusion bonding • Anodic bonding with metallic or a:Si layer                                                                                                                                                                                                                                                                              | Anodic bonding                                                                                                                                                                                                                                                                                 |  |

|      |                                                                  |                                            | The device operates at or below $\sim 200^{\circ}\mathrm{C}$ | <ul> <li>Adhesive bonding</li> <li>Anodic bonding with metallic or a:Si layer</li> <li>Fusion bonding</li> </ul>                                                                                                                                                                                                                           | • Anodic bonding • Adhesive bonding                                                                                                                                                                                                                                                            |  |

|      |                                                                  | With electrical connection                 | The device operates above $\sim\!200^{\circ}\mathrm{C}$      | <ul> <li>Anodic bonding (the thickness of the metallic layer<br/>can be critical)</li> <li>Bonding using an intermediate layer</li> </ul>                                                                                                                                                                                                  | Anodic bonding (the thickness of the metallic layer<br>can be critical)                                                                                                                                                                                                                        |  |

|      |                                                                  |                                            | The device operates at or below $\sim 200^{\circ}\mathrm{C}$ | Adhesive bonding     Anodic bonding (the thickness of the metallic layer can be critical)                                                                                                                                                                                                                                                  | Adhesive bonding     Anodic bonding (the thickness of the metallic layer can be critical)                                                                                                                                                                                                      |  |

| 4    | Fluid connections                                                |                                            |                                                              | <ul> <li>Permanent: push-fit tubing into polymer ports (optionally fix with glue or PDMS)</li> <li>Permanently attached ferrule with removable capillary tubing (e.g., Nanoport)</li> <li>Temporary: push-fit capillary tubing into PDMS device (permanent if PDMS is plasma-treated)</li> <li>Mechanically clamped chip-holder</li> </ul> |                                                                                                                                                                                                                                                                                                |  |

photolithography and to around  $0.3~\mu m$  for projection photolithography. When even smaller features are required, electron-beam or nanoimprint lithography may be used instead. The resolution of the lithography step usually provides a *lower bound* on the minimum feature size that can be achieved in the glass or silicon. Lateral etching of the mask or bulk material will generally increase the smallest achievable channel size.

# A. Glass patterning

#### 1. Wet etching

The wet-etching of glass is isotropic and is usually done with solutions of hydrofluoric acid. Glass is a mixture of oxides whose composition affects etching behavior. <sup>45</sup> It is preferable to use glass with a low content of any oxides that give insoluble products after reaction with HF. Such oxides include CaO, MgO, and Al<sub>2</sub>O<sub>3</sub>. To remove any insoluble products, HCl (Ref. 46) or H<sub>3</sub>PO<sub>4</sub> (Ref. 47) can be added to the etching solution. The etch rate is a parabolic function of HF concentration and is strongly dependent on the glass composition; for Corning 7740, the etch rate in 49% concentration HF is around 8  $\mu$ m/min (Ref. 48), while for quartz, the etching rate in the same solution is 1.3  $\mu$ m/min. Etch rate can be increased by raising the temperature of the solution, by using ultrasonic agitation or by annealing the glass wafer before etching. <sup>49</sup> Etch rate can be reduced by diluting the solution. Dilution with NH<sub>4</sub>F is preferred to dilution with water because the ammonium fluoride buffer stabilizes and increases the HF<sub>2</sub><sup>-</sup> content. Moreover, the presence of NH<sub>4</sub>F stabilizes the pH value of the solution, ensuring a constant etch rate. <sup>50</sup> Particular safety precautions must be taken when using HF solutions because of the chemical's ability to permeate skin insidiously and dissolve bone.

A key issue in the micropatterning of glass is the masking layer. It is important to control the magnitude and sign (compressive or tensile) of any residual stress in the mask, as well as any stress gradient,<sup>51</sup> and the hydrophobicity of the masking layer.<sup>49</sup> A small defect in a masking layer with tensile stress can generate cracks. If the masking layer presents a hydrophilic surface, the etching solution will easily penetrate through this crack and generate a pinhole. Many masking materials for wet etching of glass have been reported in the literature, including photoresist,<sup>52</sup> amorphous Si deposited at low  $(200 \,^{\circ}\text{C})^{53}$  or high temperatures  $(570 \,^{\circ}\text{C})$ ,<sup>54</sup> LPCVD polysilicon,<sup>55,56</sup> Cr/Au,<sup>57</sup> Cr/photoresist,<sup>58</sup> bulk Si,<sup>59</sup> amorphous SiC/PECVD,<sup>60</sup> Ag,<sup>61</sup> Mo,<sup>62</sup> and Ti.<sup>63</sup> A detailed analysis of masking materials used in wet etching of glass is presented in Ref. 45. The use of a photoresist mask is limited to shallow etching (up to a 2-min etching process in 49% HF). Photoresist, Ti, Ag, bulk Si, or even amorphous SiC masks lead to an increased isotropy of the etching process (i.e., an increased lateral etch rate), and for this reason, their application is limited. The most successful solutions involve multilayer depositions of Cr/Au/Cr/Au with photoresist, <sup>64</sup> a Cr/Au (50:1 μm) multilayer deposition with photoresist, 49 polished polysilicon (1.5  $\mu$ m-thick) with SU-8 photoresist (50  $\mu$ mthick),<sup>57</sup> low stress amorphous Si/photoresist,<sup>53</sup> and low-stress (LS) amorphous Si/low-stress SiC/photoresist.<sup>65</sup> The presence of photoresist (hard-baked) is essential due to its hydrophobic nature: the penetration of the etchant through any small defects in the masking layer becomes

The difficulties associated with forming a resilient etch-mask can be avoided by using photosensitive glass such as Foturan<sup>®</sup>,  $^{66}$  which is directly exposed with patterned ultraviolet light in the wavelength range 290–330 nm. Silver atoms form in the exposed regions of the glass, promoting crystallization when the material is subsequently heated to  $500-600\,^{\circ}$ C. The crystallized regions exhibit a 20 times higher etch-rate than the unexposed regions when etched in 10% HF at room temperature. An exposure energy density of approximately 2 J/cm² has been found sufficient to pattern a 1 mm-thick plate of this material. Feature sizes of  $25~\mu m$  and a surface roughness of 1  $\mu m$  are claimed by the material's supplier. It has also been shown that buried 3D structures such as channels, lenses, and waveguides can be directly written inside a single Foturan<sup>®</sup> sheet using a femtosecond laser. Such an approach can eliminate the need for two glass layers to be bonded, albeit at the expense of using a serial exposure technique that would be expected to be slower and more expensive than photolithography.

#### 2. Dry etching

Micropatterning of glass using dry etching processes is recommended only when an anisotropic etching profile is required on a transparent substrate. Compared to wet etching, the dry etching of glass is a relatively slow process, with etching rates of 0.5–0.7  $\mu$ m/min and poor selectivity relative to the mask. Moreover, the process, which is usually performed in inductively coupled plasma deep RIE reactors, is limited by the large amount of energy transferred to the glass material, which generates strong temperature gradients (the thermal conductivity of glass is 100 times lower than that of silicon). These temperature gradients can lead to poor control of the process and a reduced etch selectivity for glass over the masking material. They can also promote fracture of the wafer during processing. The process requires a low pressure of 5-10 mTorr, since ion bombardment of the material (physical etching) plays an important role. The gas precursors used for deep etching of glass are SF<sub>6</sub>, <sup>68,69</sup> C<sub>4</sub>F<sub>8</sub>, <sup>53,70</sup> CF<sub>4</sub>, <sup>71</sup> or CHF<sub>3</sub>. <sup>72</sup> Additional gases such as He, H<sub>2</sub>, O<sub>2</sub>, or Ar may be added to control chamber pressure or for improving the quality of the etching process. Since the selectivity of the etching process is low, a relatively thick masking layer is required, such as electroplated Ni (20  $\mu$ m-thick) for SF<sub>6</sub> chemistry, bulk silicon, <sup>71</sup> PECVD amorphous silicon (12  $\mu$ m-thick), or even a thick layer of SU-8 photoresist. The selectivity of the etching rate (glass/mask) is about 4:1 and 2.5:1 for Si and SU-8 masks, respectively.

# **B. Silicon patterning**

Silicon patterning methods suitable for microfluidic applications can be divided in two main groups, namely dry and wet etching processes. The most common, fastest, and therefore, recommended process is deep dry etching (the *Bosch process*), which is now routinely used for microfluidic applications.

#### 1. Dry etching

Dry etching processes used in microfabrication can be divided according to whether they are anisotropic or isotropic. A common isotropic dry etch uses XeF<sub>2</sub> as the precursor.<sup>73</sup> The process is mainly used for dry-release in surface micromachining.

There are two main techniques for achieving high aspect ratio structures in silicon: the Bosch process (which is the more prevalent)<sup>74</sup> and *cryogenic* etching. The Bosch process is a two-step technique involving alternate passivation and etching. For the passivation step, a  $C_4F_8$ -based plasma generates a conformal coating of a polytetrafluoroethylene (PTFE)-like fluorocarbon polymer over the exposed surfaces. In the next step, which uses fluoride chemistry (SF<sub>6</sub>), the fluoropolymer deposited on the horizontal surfaces is removed by ion bombardment and the silicon is then isotropically etched for a period of a few seconds. By repeating the passivation/etch cycles and controlling the etch time, the degree of lateral etch is limited, allowing a trench to be etched vertically through the wafer. The most common masking layers used are photoresist (selectivity 50:1) and SiO<sub>2</sub> (selectivity 200:1). In the cryogenic deep RIE process, the wafer is chilled to around  $-110\,^{\circ}$ C. The process uses SF<sub>6</sub>/O<sub>2</sub> to provide fluorine radicals for silicon etching. At the above-mentioned temperature, a layer of SiO<sub>x</sub>F<sub>y</sub> forms, providing sidewall passivation. The etched profile is very sensitive to the pressure as well as to the SF<sub>6</sub>/O<sub>2</sub> ratio. For both Bosch and cryogenic techniques, appropriate process parameters depend on the reactor design. A review of cryo-DRIE and Bosch-DRIE can be found in Ref. 75.

Oxidation of silicon after etching can help circumvent the feature-size limitations of photolithography. The growth of the oxide reduces the widths of trenches etched in silicon, which can be valuable for producing nanofluidic channels.<sup>24,25</sup>

## 2. Wet etching

There are two main options for the wet etching of silicon: orientation-dependent etching and isotropic etching. Wet etching of silicon is recommended only when a dry process is not available.

The *isotropic etching* of silicon is performed in HNA solutions (a mixture of HNO<sub>3</sub>, HF, and CH<sub>3</sub>COOH). In this redox etching reaction, HNO<sub>3</sub> oxidizes the Si surface, while HF

dissolves the generated oxide layer, and CH<sub>3</sub>COOH acts as a diluent. The HNA etching solution is very aggressive and the etching rate is strongly dependent on the concentration and temperature of the acid. A mixture of HNO<sub>3</sub> (69%) with HF (49%) in a ratio 2:1 gives etch rates of around 50  $\mu$ m/min. The aggressive etching characteristic of HNA solution reduces the range of masking layers that can be used. The best masking layer for HNA solution is LPCVD Si<sub>3</sub>N<sub>4</sub>, which has an etching rate of 1–10 nm/min. HNA

The *orientation-dependent etching* of silicon<sup>78</sup> relies on the selective etching of different crystallographic planes. A number of etchants have been used for orientation-dependent etching of silicon, the best known being aqueous potassium hydroxide (KOH) solution, most likely due to the high etching ratio of about 400 between the (100) and (111) crystallographic planes. A KOH solution of at least 20% concentration is required for a good etching process; below this concentration, the surface becomes rough and insoluble residues can be found on the surface. Another characteristic of the process is the ability to stop the etch by inserting a heavily boron-doped layer in the silicon: the etch rate reduces greatly when the doped layer is reached.

Table II summarises the capabilities of the etchants described above. We recommend wet etching of glass and deep RIE of silicon as being the most versatile and reliable of these processes. Any choice of process will, of course, depend on the application, the availability of equipment, and the total cost involved.

## C. Through-holes for fluid ports

Etched through-holes can be achieved in glass by deep wet etching (a process described above). In this case, suitable masks are Cr/Au/photoresist or LS amorphous Si (a:Si)/photoresist. Even better results can be achieved with LS a:Si/LS a:SiC/photoresist. Highly concentrated HF solution must be used as the etchant. The back-side of the wafer can be protected with a

| Etched material | Process                                         | Suitable etchants                                                                       | Suitable<br>masking layers                                                                                                                      | Etch rate                                 | Remarks                                                      |

|-----------------|-------------------------------------------------|-----------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|--------------------------------------------------------------|

| Glass           | Wet HF/HCl (10/1)<br>HF<br>HF/NH <sub>4</sub> F |                                                                                         | <ul> <li>Cr/Au/Photoresist</li> <li>Amorphous Si</li> <li>Molibdenum/photoresist</li> <li>Amorphous Si/Amorphous<br/>SiC/Photoresist</li> </ul> | Up to 7–8<br>μm/min (for<br>Corning 7740) | The process is<br>strongly dependent on<br>glass composition |

|                 | Dry                                             | SF <sub>6</sub> , C <sub>4</sub> F <sub>8</sub> , CF <sub>4</sub> ,<br>CHF <sub>3</sub> | <ul><li>Ni plated</li><li>Thick amorphous Si</li><li>SU8 resist</li></ul>                                                                       | Up to 0.5–0.8<br>μm/min                   | The process is<br>strongly dependent on<br>glass composition |

| Silicon         | Dry                                             | Bosch                                                                                   | <ul> <li>Photoresist</li> <li>SiO<sub>2</sub> (wet or PECVD)</li> </ul>                                                                         | 2–30 μm/min                               | Most recommended                                             |

|                 |                                                 | Cryogenic                                                                               | • SiO <sub>2</sub> (wet or PECVD)<br>• Metal                                                                                                    | Up to 7 $\mu$ m/min                       | Smooth walls                                                 |

|                 | Wet                                             | HNA<br>(HNO <sub>3</sub> +HF<br>+CH <sub>3</sub> COOH)                                  | • Si <sub>3</sub> N <sub>4</sub> (LPCVD)                                                                                                        | 4–90 μm/min                               | Isotropic                                                    |

|                 |                                                 | КОН                                                                                     | • Si <sub>3</sub> N <sub>4</sub> (LPCVD, PECVD)<br>• SiO <sub>2</sub> (thermal/wet)<br>• SiC (PECVD)                                            | 1.4 $\mu$ m/min in (100) direction        | Anisotropic                                                  |

|                 |                                                 | EDP                                                                                     | SiO <sub>2</sub> , Si <sub>3</sub> N <sub>4</sub> , Ta, Au, Cr, Ag,<br>Cu                                                                       | 1.25 $\mu$ m/min in (100) direction       | Anisotropic                                                  |

|                 |                                                 | ТМАН                                                                                    | SiO <sub>2</sub> , Si <sub>3</sub> N <sub>4</sub>                                                                                               | 1 $\mu$ m/min in (100) direction          | Anisotropic                                                  |

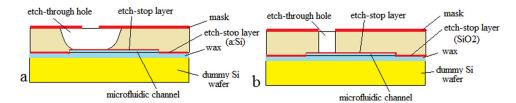

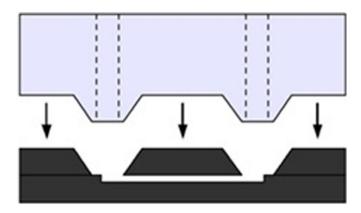

FIG. 1. Setup for etching through-holes in (a) glass and (b) silicon.

dummy silicon wafer bonded using wax (Figure 1(a)). Meanwhile, an etch-stop layer (amorphous silicon) is strongly recommended to protect the pattern on the other side of the wafer. Due to the isotropy of the process, the diameter of the generated hole is at least the diameter of the hole in the mask plus twice the wafer thickness. Several other methods have been used for patterning glass in microfluidic applications. Through-glass holes for fast prototyping can be achieved using sand-blasting, <sup>79</sup> laser-drilling, <sup>80</sup> electrochemical discharge, <sup>81</sup> or drilling with diamond beads. <sup>82</sup>

For silicon, well-dimensioned through-holes aligned within a few micrometers can be achieved using a deep RIE process. For the masking layer,  $2-3 \mu m$ -thick SiO<sub>2</sub>,  $10-15 \mu m$ -thick photoresist (according to the wafer thickness), or a double-layer mask (photoresist + SiO<sub>2</sub>) can be used. Such an arrangement is presented in Figure 1(b). As an etch-stop layer, SiO<sub>2</sub> (PECVD) or tetraethyl orthosilicate (TEOS) can be used  $(0.2-0.5 \mu m \text{ thick})$ . This layer helps to avoid deterioration through the notching effect of the structure on the back of the wafer. For the final part of the etching process (the last  $50-100 \mu m$ ), a dummy handle wafer can be attached with wax in order to avoid deterioration of the wafer's chuck.

#### D. Bonding

Wafer-bonding methods suitable for microfluidic applications can be categorized as *direct* (including fusion processes), *anodic*, and *adhesive*. Several factors must be taken into account in choosing a bonding process. These factors include the thermal coefficients of expansion of the materials to be bonded, their surface chemistries, temperature limitations resulting from earlier steps in the fabrication process, the presence of any metallic layers, price, throughput, and yield. Bonding processes are summarised in Table III.

## 1. Direct bonding

Two glass surfaces, mirror-polished (R<sub>a</sub>=1.5-2 nm) and with good planarity placed in contact at room temperature, will adhere due to the van der Waals force. In this case, the bond strength is weak (the shear stress supported by such a bond has been measured as 0.6 MPa (Ref. 83)). Direct bonding requires a good cleaning procedure to avoid contamination, and for this reason, it can be helpful to bring the surfaces to be bonded into contact under a continuous flow of deionised water. The bonding strength can be increased by activation of the surfaces and by annealing. Allen and Chiu<sup>84</sup> propose activation of the glass surface in a calcium solution followed by annealing for 1-2 h at 115 °C. Plasma activation, which is frequently used for PDMS/glass bonding, so can also be used to increase the bond strength. Howlader *et al.* propose nitrogen radical activation of the glass surfaces in a microwave reactor after an oxygen RIE treatment. They found that the glass must be subsequently heated to above 400 °C with the surfaces in contact to bring about a significant increase of the bond strength. With an annealing temperature of 600 °C, a bond strength of around 24 MPa was attained.

Fusion bonding of Pyrex glass wafers (Corning 7740) can be performed at a temperature of 650 °C. 54,87,88 The wafers can be bonded in an annealing furnace. A slow cooling rate is required because glass wafers may fracture if exposed to substantial temperature gradients. The wafers must be horizontally supported during bonding to avoid deformation. At 650 °C, the glass is softened and the two surfaces to be bonded can readily conform, compensating for any roughness or the presence of metallization patterns at the interface.

TABLE III. Summary of bonding techniques with typical parameters (parameters may need to be varied according to the application).

| Method            |                                         | Materials                       | Process parameters                                                                            | Remarks                                                                                                              |  |

|-------------------|-----------------------------------------|---------------------------------|-----------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------|--|

| Direct<br>bonding | Plasma-activated Glass/glass<br>bonding |                                 | $115400^{\circ}\text{C}$ , $N_2/O_2$ plasma activation of the surface                         | Weak bonding, the quality of the bonding process can be improve by annealing at 600 °C                               |  |

|                   | Fusion bonding                          | Glass/glass                     | 650°C                                                                                         | Strong bonding, special attention<br>must be given to the plastic flow<br>of the glass                               |  |

| Anodic<br>bonding |                                         | Glass/silicon                   | 305–350 °C, 0.05 MPa, 1000 V                                                                  | Strong bonding with a good yield can be performed over SiO <sub>2</sub> layers (up to 600 nm thick)                  |  |

|                   |                                         | Glass/silicon/<br>glass         | First bonding: 305–350 °C, 0.15 MPa, 1000 V Second bonding: 450 °C, 0.3 MPa, 1500 V           | First bonding must be incomplete<br>in order to keep the glass wafer<br>conductive at relatively high<br>temperature |  |

| Adhesive bonding  | SU8                                     | Glass/glass or<br>glass/silicon | 150 °C, 0.15 MPa N (4 in. wafer),<br>30 min                                                   | The SU8 layer can be imprinted on the surface to be bond                                                             |  |

|                   | Parylene                                |                                 | $280$ – $350^{\circ}$ C, $0.15$ MPa, $2~\mu$ m-thick parylene                                 | Good quality bonding with high<br>yield can be performed over<br>metals layers                                       |  |

|                   | ВСВ                                     |                                 | 200–300 °C, 1–2 h, 0.15–0.25 MPa, in vacuum                                                   | Good quality bonding can be performed over metals layers                                                             |  |

|                   | Polyimide                               |                                 | 180–400 °C, 1–3 h, in vacuum,<br>0.15–0.35 MPa surface preparation<br>(O <sub>2</sub> plasma) | Bond strength $\sim$ 8 MPa,<br>Recommended at chip size                                                              |  |

# 2. Anodic bonding

Anodic bonding is a process that can be used to seal a glass cover to a patterned silicon wafer.  $^{90}$  It is the simplest way of achieving a glass/silicon microfluidic device. The thermal expansion coefficient of the glass wafer must match that of the silicon in order to avoid cracks in the bonded wafers. Not all types of glass are bondable to silicon, a condition being the presence of  $Na_2O$  in the glass composition. Under the high voltage and temperature,  $Na^+$  migrates to the negative electrode, generating a strong electrostatic force and an irreversible chemical bonding between the substrates. The most commonly used are: Corning 7740, Borofloat and Tempax (Schott), and SD2 and SD4 (Hoya). The cleaning process of the wafer before bonding is a critical step for a good anodic bonding process.

Early work on the optimization of anodic bonding conditions for low residual stress is presented by Rogers and Kowal. <sup>91</sup> The necessary bonding conditions depend on the glass material used. For Corning 7740, the optimal conditions are 305–350 °C and 500 V for 15 min (Ref. 92) and the necessary applied pressure is 0.05 MPa. At this bonding temperature, the expansions of silicon and glass are sufficiently similar. Meanwhile for Corning 7070, a glass with high resistivity, the optimal conditions were found to be 400 °C and 4 kV applied for 20 min at similar applied pressure. The presence of any dielectric layer (SiO<sub>2</sub>) on the silicon substrate may require a higher applied voltage. <sup>93</sup>

Glass/glass anodic bonding can also be carried out using Ti (80 nm thick) as a metallic intermediate layer. <sup>94</sup> The bonding connections reported for this work were a temperature of 530 °C and an applied voltage of 100 V; Corning 0021 microscope slides were used. With the Ti thickness of 80 nm, the bonded sample was still transparent. A patterned Ti/Pt intermediate layer has been used to form electrodes in a glass device, at the same time as enabling anodic

bonding of the glass layers. 95 Amorphous silicon has also been used as an intermediate layer for anodic bonding processes. 96,97

# 3. Glass/silicon/glass structures

Another structure of interest for transparent microfluidic devices is glass/silicon/glass,  $^{98,99}$  where the glass layers form the ceiling and the floor of the microfluidic channel, while the silicon defines the walls. The microfluidic channels are defined using a deep RIE process (in this case, a small notching effect can occur at the silicon-glass interface  $^{100}$ ). In order to perform a double anodic bonding, the first bonding process must be incomplete so that the wafer pair remains somewhat conductive. This can be accomplished by stopping the first bonding process when the current has fallen to  $\sim 40\%$  of its initial value. A low bonding temperature of  $305\,^{\circ}$ C and an applied pressure of  $0.15\,^{\circ}$ MPa must be used. For the second bonding, the temperature is increased to  $450\,^{\circ}$ C, the voltage to  $1500\,^{\circ}$ V, and the applied pressure to around  $0.3\,^{\circ}$ MPa, to allow some plastic flow of the glass and compensate for the deformation of the bonded wafers. Higher temperature also increases the conductivity of the stack, promoting the anodic bonding process.  $^{100}$

#### 4. Adhesive bonding

Adhesive bonding is well suited to microfluidic applications, because the adhesive layer between the bonded wafers is able to conform easily to the topography of any metallization layer patterned at the interface. Moreover, adhesive bonding is a simple, robust, and low-cost process. A review of the use of adhesive bonding in MEMS is presented in Ref. 101. The polymers used in adhesive bonding for microfluidic applications are usually thermoplastic materials (which can be repeatedly softened by heating and solidified by cooling) or thermosetting materials (which form a 3D network by cross-linking and cannot be remelted). Various adhesives have been used in microfluidic applications, including Parylene C, UV-curing epoxies (e.g., SU-8), benzocyclobutene (BCB), and polyimide. The main steps of an adhesive bonding process are

- · surface cleaning,

- surface treatment (some polymer surfaces need to be treated with an adhesion promoter),

- coating with the adhesive layer (on one or both surfaces),

- baking process (optional),

- patterning (optional),

- bonding (usually using a bonding tool, under vacuum and an applied pressure).

A contact imprinting process has been demonstrated in which a SU-8 adhesive layer is applied only to those regions of the wafer that are to be bonded, keeping the adhesive out of the microfluidic channels. The bonding is performed at 150 °C for 30 min with an applied pressure of 0.15 MPa. The quantity of SU-8 applied must be very well controlled in order to avoid flow of the adhesive material into the microfluidic channels, and the technique depends on the operator's skill. A similar "stamp-and-stick" procedure using UV-curable adhesive to bond glass devices has also been presented. <sup>103</sup>

Parylene is a thermoplastic material which has been used in MEMS wafer-bonding processes. 104 The material has been applied to microfluidic device fabrication for bonding glass to glass 105 and glass to silicon 106 at temperatures of 280–350 °C. Parylene has seen other microfluidic applications as well. 107,108 The main advantages of Parylene C are its good thermal stability, good chemical resistance, and relatively strong bonding compared with SU-8: pull tests have shown a bonding strength of around 10 MPa and a maximum burst pressure of 7.6 MPa (Ref. 106). Parylene can be deposited in thin layers by chemical vapour deposition and can be patterned by dry etching through a photoresist mask. We have found that, with parylene, an areal bonding yield of greater than 90% is possible, which is comparable with anodic bonding. 106

BCB is another polymer that has been used for wafer bonding.<sup>109</sup> It can be made photosensitive or can be patterned by dry etching through a photoresist mask. BCB offers good chemical

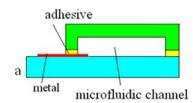

FIG. 2. Electrical feedthrough approaches: (a) lateral and (b) vertical. After the principle described by Esashi in Ref. 121.

resistance to acids, alkalis, and solvents, and is transparent to visible light. BCB can be applied by spin-coating and its use in microfluidic applications is presented in Refs. 110 and 111. The material is applied on one or both surfaces and is then pre-baked for a few minutes at 100–170 °C in order to remove the solvent, yet avoid cross-linking. Good bonding can be achieved at temperatures of 200–300 °C for 1–2 h, in vacuum with an applied pressure of 0.15–0.5 MPa; 102,112 at these temperatures, the material reaches a low-viscosity state while cross-linking.

*Polyimides* are thermosetting and thermoplastic materials, suitable for microfluidic applications. <sup>113,114</sup> During the curing process, voids tend to form in the polymeric film, and for this reason, polyimide is recommended for bonding at the chip scale. <sup>102</sup> Polyimide can be spin-coated, followed by a baking process. Both surfaces to be bonded must be coated with polyimide. Depending on the material characteristics, the curing temperature can be 150–400 °C applied for 1.5–3 h at a pressure of 0.15–0.35 MPa (Ref. 115).

## E. Electrode integration

Some microfluidic applications require the incorporation of electrodes. Examples are the electrical characterization of biological samples by impedance spectroscopy, <sup>116</sup> particle manipulation by dielectrophoresis, <sup>117–119</sup> and microfluidic fuel cells. <sup>120</sup> Any electrodes placed inside microfluidic channels must usually be connected to the outside world. As described by Esashi, <sup>121</sup> there are two main techniques that can be used for such connections

Lateral feedthrough techniques (Figure 2(a)). Corman et al.<sup>122</sup> have demonstrated anodic bonding over a metallization layer patterned on the glass substrate. The thickness of the metal layer was 25 nm (Cr/Au). Alternatively, most adhesive bonding methods can accommodate lateral feedthrough of metallization.<sup>40,80,81</sup>

Vertical feedthrough techniques (Figure 2(b)). Methods for making electrical connections through via-holes have been proposed. <sup>123</sup> In one example, metallized via holes were fabricated in a glass substrate that had been polished to a thickness of 100–150  $\mu$ m (Refs. 124 and 125) followed by isotropic wet etching through a Cr/Au mask. The electrodes themselves served as an etch-stop for the backside glass etching process. This approach, however, is more complex to achieve than lateral feedthrough.

#### **IV. WORLD-TO-CHIP CONNECTIONS**

In deciding how to connect a silicon/glass microfluidic device to the outside world, several questions must be answered

- Is the microfluidic device re-usable or disposable? In other words: how frequently do world-tochip connections need to be broken and re-made?

- Will the connections be made to the edge or the surface of the device (in-plane or out-of-plane)?

- Does the world-to-chip connection system need to be reconfigurable or is it application-specific?

Additional factors to be considered include:

- the amount of chip area used by the interconnections;

- any requirements imposed by the connection system on the chip fabrication process;

- pressure tolerance;

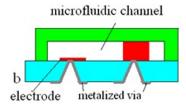

FIG. 3. Basic configurations of fluidic interconnects: (a) out-of-plane (top connector) and (b) in-plane (edge connector). The capillary is drawn showing both inner and outer diameters.

- temperature tolerance;

- · compatibility of materials used;

- · dead volume;

- · price;

- · usability.

Fluidic ports are often fabricated by conventional machining techniques, such as drilling or powder-blasting, and, if so, their dimensional and positional accuracies are much less than those of the microfluidic channels. As shown in Figure 3(a), port-to-microchannel misalignment can lead to dead volume.

Permanent attachment comes in two major forms: direct attachment of capillary tubing to the chip or permanent attachment of a fitting (or ferrule) to the chip, with the capillary being either permanently or temporarily attached to the fitting. It is sometimes possible to make out-of-plane connections by a simple push-fit between the capillary-tube and the chip, but such an attachment is usually mechanically too weak (polymer chips which can easily be 2–5 mm thick are more amenable to this sort of tube fitting <sup>126</sup>). Gluing, melting, <sup>127</sup> and PDMS casting can be used to reinforce the connection, but may clog delicate microfluidic channels, leading to yield losses.

Commercial fittings from Upchurch, <sup>128</sup> Swagelok, <sup>129</sup> and Valco<sup>130</sup> are available for out-of-plane connections. They are universal in the sense that the fluidic design is done completely independently of the connectors. These fittings allow for detachment of tubing. The two basic varieties of tube contact are flat and coned; the coned variety is suitable for higher pressures. Individual connectors cost up to \$20, which can constitute a sizable portion of a fluidic system's cost.

Non-permanent attachment often makes use of the self-adhesive property of PDMS. In one implementation (Figure 4), an anisotropically etched silicon chip was itself used as a master

FIG. 4. A PDMS connector makes intimate contact with the silicon chip because a dummy replica of the chip itself was used as a mould master Reprinted with permission from Saarela *et al.*, Sens. Actuators B **114**, 552 (2005). Copyright © 2005, Elsevier.

mould for creating a matching PDMS piece. <sup>131</sup> Dummy capillaries were inserted into the PDMS before curing. Both the connector and the capillaries can be detached and reinserted as long as the PDMS remains clean enough. If higher pressure tolerance is required, PDMS may be plasma-treated, but then a permanent bond is created. This connector results in extremely small dead volumes because all the structures are microfabricated. Non-permanent connectors have also been demonstrated using polyolefin heat-shrink tubing. <sup>132</sup>

Various custom-made chip holders are in use. These holders are typically made of steel, brass, or ceramics like Macor, and incorporate o-rings for sealing and some sort of mechanical tightening. This approach can benefit from inlet/outlet standardization: if inlets/outlets are only allowed at predetermined positions, the same holder works for many designs. An alternative, which is suitable for fast-changing prototype designs, is to use magnetic connectors. A capillary is inserted inside a ring magnet, which is held in place by placing another magnet on the opposite side of the chip. This approach allows quick and easy testing. Limitations include magnet-magnet interactions, which limit closely spaced inlets, and the inability to handle fluids containing magnetic particles. Fluidic probe stations are stations are made with probe-heads, similar to electric probe needles, and pressure is applied mechanically to ensure leak-free connection. The system is best suited for applications with few inlets/outlets. Mechanical non-permanent connectors are difficult to implement for high-density inlets.

In-plane (edge) connection can be done simply by inserting the capillary into the on-chip fluidic channel (Figure 3(b)). Capillary outer diameters (ODs) are in the range of  $100-300~\mu m$ , and fluidic channels must match those dimensions, which may add process steps in chip fabrication. Additionally, capillary inner diameters are typically  $50~\mu m$ , and considerable dead volume may be introduced when a large OD capillary must be matched with much smaller on-chip channels. Another feature that might be needed is an on-chip stopper structure (Figure 3(b)). This stopper ensures that capillary insertion is self-limited and reproducible. Gluing is often used to fix the capillary in place. Dicing of silicon and glass is well established, and the high quality of diced edges allows them to be used as active parts of devices, including as interconnection sites.

Fluidic connections must sometimes sustain considerable pressures, e.g., in liquid chromatography. Pressures in the 100 bars range pose no problems for silicon and glass devices themselves; rather the connections become the limiting factor. For instance, soft o-rings, which accommodate surface irregularities, are not applicable in high-pressure applications.

Materials compatibility is especially important when aggressive solvents or high temperatures are used. Glues or PDMS can leach into fluidic channels, potentially ruining sensitive analyses.

## V. CONCLUDING REMARKS

This paper has reviewed the state of the art in glass and silicon bulk micromachining and has aimed to provide the reader with enough information to conceive a suitable process flow for their own glass/silicon microfluidic application.

There are three main approaches to making glass/silicon-based micro- and nano-fluidic devices: surface micromachining, "buried-channel" technologies, and bulk micromachining. In this paper, we have focused on bulk micromachining, which is the most widely used approach.

For bulk micromachining, our analysis of the available etching, bonding, and interconnection techniques suggests two basic processing routes: one in which the device is constructed from a pair of glass layers and another in which a glass layer is bonded to a silicon one. Recommended sets of processes for the two routes are summarised in Table I.

For patterning *glass*, wet HF/HCl etching is recommended. Plasma etching may offer more vertical feature sidewalls and higher aspect-ratio structures, but remains slow and hard to control for glass. For silicon, in contrast, deep reactive ion etching is now a mature process and is recommended over wet etching. Suitable wet and dry etchants and masking layers for both silicon and glass are summarised in Table II.

The choice of bonding method depends on the chosen materials, the device's final operating temperature, and the presence or absence of integrated electrodes. Adhesive bonding is generally inexpensive and can readily conform to a patterned electrode layer at the interface, but is appropriate only up to operating temperatures of  $\sim 200\,^{\circ}$ C. For higher operating temperatures, anodic or fusion bonding is preferred; if anodic bonding is used with two glass layers, an interfacial conductive layer is needed. Parameters are recommended in Table III.

For inserting and removing fluids to and from a device, a wide variety of permanent and re-adjustable attachment schemes has been tried. Although there have been some attempts to commercialise microfluidic packaging systems, there is still plenty of scope for innovation in this area.

This paper has focused mainly on the production of devices with features that are more than a micrometer in size. We have, however, also touched on *nanofluidic* applications in which channels need to be sub-micrometer in depth, width, or both. Bulk micromachining is not an attractive way of producing nanochannels with a precisely controlled *depth*; for that purpose, surface micromachining is more promising. For deeper, sub-micrometer-*width* channels, however, bulk micromachining can be appropriate if the lithography step offers sufficient lateral resolution, or if feature widths are reduced to the desired value by post-etching oxidation. There is much work to be done to develop micro- and nano-fluidic fabrication techniques further and to integrate features with widely ranging length-scales into glass/silicon devices.

#### **ACKNOWLEDGMENTS**

J. Microelectromech. Syst. 15, 1251 (2006).

We acknowledge funding support from the Institute of Bioengineering and Nanotechnology (C.I.), Singapore, the Singapore–MIT Alliance for Research and Technology (H.T.), and SOP-IEC Project, O.2.1.2, No.209, ID 665 (M.A.).

```

<sup>1</sup>L. Y. Yeo, H.-C. Chang, P. P. Y. Chan, and J. R. Friend, Small 7, 12 (2011).

<sup>2</sup>D. Mark, S. Haeberle, G. Roth, F. von Stetten, and R. Zengerle, Chem. Soc. Rev. 39(3), 1153 (2010).

<sup>3</sup>M. Ni, W. H. Tong, D. Choudhury, N. A. A. Rahim, C. Iliescu, and H. Yu, Int. J. Mol. Sci. 10(12), 5411 (2009).

<sup>4</sup>S. Marre and K. F. Jensen, Chem. Soc. Rev. 39(3), 1183 (2010).

<sup>5</sup>S. C. Terry, J. H. Jerman, and J. B. Angell, IEEE Trans. Electron Devices 26(12), 1880 (1979).

<sup>6</sup>A. Manz, Y. Miyahara, J. Miura, Y. Watanabe, H. Miyagi, and K. Sato, Sens. Actuators, B 1(1-6), 249 (1990).

<sup>7</sup>P. Abgrall and A.-M. Gue, J. Micromech. Microeng. 17, R15 (2007).

<sup>8</sup>H. Becker and C. Gärtner, Anal. Bioanal. Chem. 390, 89 (2008).

<sup>9</sup>D. C. Duffy, J. C. McDonald, O. J. A. Schueller, and G. M. Whitesides, Anal. Chem. 70(23), 4974 (1998).

<sup>10</sup>T. Thorsen, S. J. Maerki, and S. R. Quake, Science 298(5593), 580 (2002).

<sup>11</sup>M. Unger, H.-P. Chou, T. Thorsen, A. Scherer, and S. Quake, Science 288(5463), 113 (2000).

<sup>12</sup>P. Mao, "Fabrication and characterization of nanofluidic channels for studying molecular dynamics in confined environ-

ments" S.M. thesis, Massachusetts Institute of Technology, Cambridge, MA, 2005.

<sup>13</sup>H. Becker, Lab Chip 10, 271 (2010).

<sup>14</sup>C. F. Carlborg, T. Haraldsson, K. Öberg, M. Malkoch, and W. van der Wijngaart, Lab Chip 11, 3136 (2011).

<sup>15</sup>D. Brassard, L. Clime, K. Li, M. Geissler, C. Miville-Godin, E. Roy, and T. Veres, Proceedings of MicroTAS 2011, 2–6

October 2011, Seattle, WA, USA.

<sup>16</sup>D. E. Hardt, B. W. Anthony, and S. B. Tor, International Symposium on Nanomanufacturing (ISNM 2008), 23–25

January 2008, Singapore.

17S. Franssila and S. Tuomikoski, "MEMS lithography," in Handbook of Silicon Based MEMS Materials and Technolo-

gies, edited by V. Lindroos, M. Tilli, A. Lehto, and T. Motooka (Elsevier, New York, 2010). <sup>18</sup>S. Tuomikoski and S. Franssila, Sens. Actuators, A 120, 408 (2005).

<sup>19</sup>N.-T. Nguyen, T.-Q. Truong, and K.-K. Wong, J. Micromech. Microeng. 14, 69 (2004).

<sup>20</sup>T. Sikanen, L. Heikkilä, S. Tuomikoski, R. A. Ketola, R. Kostiainen, S. Franssila, and T. Kotiaho, Anal. Chem. 79(16),

6255 (2007).

<sup>21</sup>S. Tuomikoski, T. Sikanen, R. Ketola, R. Kostiainen, T. Kotiaho, and S. Franssila, Electrophoresis 26, 4691 (2005).

<sup>22</sup>J. El-Ali, I. R. Perch-Nielsen, C. R. Poulsen, D. D. Bang, P. Telleman, and A. Wolff, Sens. Actuators, A 110, 3 (2004).

<sup>23</sup>A. W. Martinez, S. T. Phillips, and G. M. Whitesides, Proc. Natl. Acad. Sci. U.S.A. 105(50), 19606 (2008).

<sup>24</sup>J. Fu, P. Mao, and J. Han, Trends Biotechnol. 26(6), 311 (2008).

<sup>25</sup>J. Han, P. Mao, and J. Fu, ECS Meeting Abstracts, 602(24), 1194 (2006).

<sup>26</sup>J. Pipper, M. Inoue, L. F. P. Ng, P. Neuzil, Y. Zhang, and L. Novak, Nat. Med. 13, 1259 (2007).

<sup>27</sup>R. M. Tiggelaar, P. van Male, J. W. Berenschot, J. G. E. Gardeniers, R. E. Oosterbroek, M. H. J. M. de Croon, J. C.

Schouten, A. van den Berg, and M. C. Elwenspoek, Sens. Actuators, A 119, 196 (2005).

<sup>28</sup>D. J. Laser and J. G. Santiago, J. Micromech. Microeng. 14, R35 (2004).

<sup>29</sup>K. W. Oh and C. H. Ahn, J. Micromech. Microeng. 16, R13 (2006).

```

<sup>30</sup>S. Franssila, S. Marttila, K. Kolari, P. Östman, T. Kotiaho, R. Kostiainen, R. Lehtiniemi, C.-M. Fager, and J. Manninen,

(2010).

```

<sup>31</sup>Y. Nakashima and T. Yasuda, Sens. Actuators, A 139, 252 (2007).

<sup>32</sup>L. Sainiemi, T. Nissilä, R. Kostiainen, R. A. Ketola, and S. Franssila, Lab Chip 11, 3011 (2011).

<sup>33</sup>D. J. Harrison, K. Fluri, K. Seiler, Z. H. Fan, C. S. Effenhauser, and A. Manz, Science 261, 895 (1993).

<sup>34</sup>C. J. Easley, J. A. C. Humphrey, and J. P. Landers, J. Micromech. Microeng. 17, 1758 (2007).

35A. C. Lewis, J. F. Hamilton, C. N. Rhodes, J. Halliday, K. D. Bartle, P. Homewood, R. J. P. Grenfell, B. Goody, A. M.

Harling, P. Brewer, G. Vargha, and M. J. T. Milton, J. Chromatogr. A 1217, 768 (2010).

<sup>36</sup>M.-S. Kim, S. I. Cho, K.-N. Lee, and Y.-K. Kim, Sens. Actuators B 107, 818 (2005).

<sup>37</sup>C. D. James, M. Okandan, S. S. Mani, P. C. Galambos, and R. Shul, J. Micromech. Microeng. 16(10), 1909 (2006).

<sup>38</sup>I. Papautsky, J. Brazzle, H. Swerdlow, and A. B. Frazier, J. Microelectromech. Syst. 7(2), 267 (1998).

<sup>39</sup>P. Abgrall and N.-T. Nguyen, Anal. Chem. 80, 2326 (2008).

<sup>40</sup>M. J. de Boer, R. W. Tjerkstra, J. W. Berenschot, H. V. Jansen, G. J. Burger, J. G. E. Gardeniers, M. Elwenspoek, and

A. van den Berg, J. Microelectromech. Syst. 9, 94 (2000).

<sup>41</sup>S.-J. Paik, S. Byun, J.-M. Lim, Y. Park, A. Lee, S. Chung, J. Chang, K. Chun, and D. Cho, Sens. Actuators, A 114, 276

(2004).

<sup>42</sup>M. Dijkstra, M. J. de Boer, J. W. Berenschot, T. S. J. Lammerink, R. J. Wiegerink, and M. Elwenspoek, J. Micromech.

Microeng. 17, 1971 (2007).

<sup>43</sup>D. J. Quinn, S. M. Spearing, M. F. Ashby, and N. A. Fleck, J. Microelectromech. Syst. 15(5), 1039 (2006).

<sup>44</sup>M. Madou, Fundamentals of Microfabrication, 2nd ed. (CRC, New York, 2002).

<sup>45</sup>C. Iliescu, B. T. Chen, and J. M. Miao, Sens. Actuators, A 143, 154 (2008).

<sup>46</sup>C. Iliescu, J. Jing, F. E. H. Tay, J. Miao, and T. T. Sun, Surf. Coat. Technol. 198, 314 (2005).

<sup>47</sup>A. Berthold, F. Laugere, H. Schellevis, C. R. de Boer, M. Laros, R. M. Guijt, P. M. Sarro, and M. J. Vellekoop, Electro-

phoresis 23, 3511 (2002).

48 K. R. Williams, K. Gupta, and M. Wasilik, J. Microeletromech. Syst. 12, 761 (2003).

<sup>49</sup>F. E. H. Tay, C. Iliescu, J. Jing, and J. Miao, Microsyst. Technol. 12, 935 (2006).

<sup>50</sup>I. Steingoetter and H. Fouckhardt, J. Micromech. Microeng. 15, 2130 (2005).

<sup>51</sup>C. Iliescu, J. Miao, and F. E. H. Tay, Sens. Actuators, A 117, 286 (2005).

<sup>52</sup>C. Iliescu, F. E. H. Tay, and J. M. Miao, Sens. Actuators, A 133, 395 (2007).

<sup>53</sup>C. Iliescu and B. T. Chen, J. Micromech. Microeng. 18, 15024 (2008).

<sup>54</sup>V. Saarela, M. Haapala, R. Kostiainen, T. Kotiaho, and S. Franssila, Lab Chip 7, 644 (2007).

<sup>55</sup>M. Stjernströ and J. Roeraade, J. Micromech. Microeng. 8, 33 (1998).

<sup>56</sup>M. A. Grétillat, F. Paoletti, P. Thiébaud, S. Roth, M. Moudelka-Hep, and N. F. de Rooij, Sens. Actuators, A 60, 219 (1997).

<sup>57</sup>D. C. S. Bien, P. V. Rainey, S. J. M. Mitchel, and H. S. Gamble, J. Micromech. Microeng. 13, S34 (2003).

<sup>58</sup>R. Mazurczyk, J. Vieillard, A. Bouchard, B. Hannes, and S. Krawczyk, Sens. Actuators B 118, 11 (2006).

<sup>59</sup>T. Corman, P. Enokson, and G. Stemme, J. Micromech. Microeng. 8, 84 (1998).

<sup>60</sup>H. Zhang, H. Guo, Z. Chen, G. Zhang, and Z. Li, J. Micromech. Microeng. 17, 775 (2007).

<sup>61</sup>H. W. Lee, D. C. S. Bien, S. A. M. Badaruddin, and A. S. Teh, Electrochem. Solid-State Lett. 13, H399 (2010).

<sup>62</sup>F. Ceyssens and R. Puers, J. Micromech. Microeng. 19, 067001 (2009).

<sup>63</sup>N. Pekas, Q. Zhang, M. Nannini, and D. Juncker, Lab Chip 10, 494 (2010).

<sup>64</sup>M. Bu, T. Melvin, G. J. Ensell, J. S. Wilkinson, and A. G. R. Evans, Sens. Actuators, A 115, 476 (2004).

<sup>65</sup>C. Iliescu, D. P. Poenar, M. Carp, and F. C. Loe, Sens. Actuators B 123, 168 (2007)

<sup>66</sup>See http://www.mikroglas.com/index.php?PAGE_ID=538# for processing information for Foturan(R) glass.

<sup>67</sup>Z. Wang, K. Sugioka, and K. Midorikawa, Appl. Phys. A 89, 951 (2007).

<sup>68</sup>X. Li, T. Abe, and M. Esashi, J. Microelectromech. Syst. 1, 625 (2002).

<sup>69</sup>J. H. Park, N.-E. Lee, J. C. Lee, J. S. Park, and H. D. Park, Microelectron. Eng. 82, 119 (2005).

<sup>70</sup>K. Kolari, V. Saarela, and S. Franssila, J. Micromech. Microeng. 18, 064010 (2008).

<sup>71</sup>A. Baram and M. Naftali, J. Micromech. Microeng. 16, 2287 (2006).

<sup>72</sup>T. Akashi and Y. Yoshimura, J. Micromech. Microeng. 16, 1051 (2006).

<sup>73</sup>C. Easter and C. B. O'Neal, J. Microelectromech. Syst. 18, 1054 (2009).

<sup>74</sup>F. Lä and A. Schilp, patents DE4241045 (1994), U.S. 5501893 (26 March 1996), and EP 625285 (1992).

75H. V. Jansen, M. J. de Boer, S. Unnikrishnan, M. C. Louwerse, and M. C. Elwenspoek, J. Micromech. Microeng. 19,

033001 (2009).

<sup>76</sup>B. Schwartz and H. Robbins, J. Electrochem. Soc. 108, 365 (1961).

<sup>77</sup>W. Kern and C. A. Deckert, "Chemical etching," in Thin Film Processes, edited by J. L. Vossen, and W. Kern (Academic,

Orlando, 1978).

<sup>78</sup>J. Haneveld, H. Jansen, E. Berenschot, N. Tas, and M. Elwenspoek, J. Micromech. Microeng. 13, S62 (2003).

<sup>79</sup> A. G. Pawlowski, E. Belloy, A. Sayah, and M. A. M. Gijs, Microelectron. Eng. 67-68, 557 (2003).

<sup>80</sup>S. W. Youn, M. Takahashi, H. Goto, and R. Maeda, Microelectron. Eng. 83(11-12), 2482 (2006).

<sup>81</sup>D. J. Kim, Y. Ahn, S. H. Lee, and Y. K. Kim, Int. J. Mach. Tools Manuf. 46, 1064 (2006).

<sup>82</sup>D. G. Grossman, Vacuum 28(2), 55 (1978).

<sup>83</sup>Z.-J. Jia, Q. Fang, and Z.-L. Fang, Anal. Chem. 76, 5597 (2004).

<sup>84</sup>P. B. Allen and D. T. Chiu, Anal. Chem. 80, 7153 (2008).

<sup>85</sup>J. R. Friend and L. Yeo, Biomicrofluidics 4, 026502 (2010).

<sup>86</sup>M. M. R. Howlader, S. Suehara, and T. Suga, Sens. Actuators, A 127, 31 (2006).

<sup>87</sup>J. Lichtenberg, E. Verpoorte, and N. F. de Rooij, Electrophoresis 22, 258 (2001).

88V. Saarela, M. Haapala, R. Kostiainen, T. Kotiaho, and S. Franssila, J. Micromech. Microeng. 19, 055001 (2009).

<sup>89</sup>V. Saarella, "Microfabrication of heated Nebulizer chips for mass spectrometry," Ph.D. dissertation (Aalto University,

2010).

90 J. Liu, J. Shang, J. Tang, and Q.-A. Huang, J. Microelectromech. Syst. 20(4), 909 (2011).

<sup>91</sup>T. Rogers and J. Kowal, Sens. Actuators, A 46, 113 (1995).

92 M. Haapala, V. Saarela, J. Pól, K. Kolari, T. Kotiaho, S. Franssila, and R. Kostiainen, Anal. Chim. Acta 662, 163

```

```

93D. Resnik, D. Vrtacnik, U. Aljancic, and S. Amon, Sens. Actuators, A 80, 68 (2000).

<sup>94</sup>P. Mrozek, Sens. Actuators, A 151, 77 (2009).

95C. Iliescu. D. P. Poenar, and S. T. Selvan, J. Micromech. Microeng. 20(2), 022001 (2010).

<sup>96</sup>A. Datta, S. Gangopadhyay, H. Temkin, Q. S. Pu, and S. R. Liu, Talanta 68, 659 (2006).

97P. Svarnas, A. Plecis, C. Nanteuil, D. Duong, C. David, M. Muller, and Y. Chen, Eur. Phys. J.: Appl. Phys. 44, 245

98 F. E. H. Tay, L. Yu, A. J. Pang, and C. Iliescu, Electrochim. Acta 52, 2862 (2007).

<sup>99</sup>C. Iliescu, G. Tresset, and G. L. Xu, Appl. Phys. Lett. 90, 234104 (2007).

100 C. Iliescu, G. L. Xu, V. Samper, and F. E. H. Tay, J. Micromech. Microeng. 15, 494 (2005).

<sup>101</sup>F. Niklaus, G. Stemme, J.-Q. Lu, and R. J. Gutmann, J. Appl. Phys. 99, 031101 (2006).

<sup>102</sup>L. Yu, F. E. H. Tay, G. Xu, B. T. Chen, M. Avram, and C. Iliescu, J. Phys.: Conf. Ser. 34, 776 (2006).

103 S. Carroll, M. M. Crain, J. F. Naber, R. S. Keynton, K. M. Walsh, and R. P. Baldwin, Lab Chip 8, 1564 (2008).

H. Kim and K. Najafi, J. Microelectromech. Syst. 14, 1347 (2005).

<sup>105</sup>D. P. Poenar, C. Iliescu, M. Carp, A. J. Pang, and K. J. Leck, Sens. Actuators, A 139, 162 (2007).

<sup>106</sup> A. T. Ciftlik and M. A. M. Gijs, J. Micromech. Microeng. 21, 035011 (2011).

<sup>107</sup>D. Ziegler, T. Suzuki, and S. Takeuchi, J. Microelectromech. Syst. 15, 1477 (2006).

<sup>108</sup>G. Yilmaz, A. T. Ciftlik, and H. Kulah, Biotechnol. J. 6, 185 (2011).

<sup>109</sup>Q. Wu, N. Lorenz, and D. Hand, Microsyst. Technol. 15, 1051 (2009).

<sup>110</sup>X. Zhou, S. Virasawmy, and C. Quan, Microsyst. Technol. 15, 573 (2009).

111 D.-H. Choi, C.-H. Yeo, J.-T. Kim, C.-W. Ok, J.-S. Kim, Y. Kwon, and Y.-H. Im, J. Micromech. Microeng. 19, 075013

(2009).

112 Y. Zhang, F. Bottausci, M. Rao, E. Parker, I. Mezic, and N. MacDonald, Biomed. Microdevices 10, 509 (2008).

<sup>113</sup>S. Metz, S. Jiguet, A. Bertsch, and P. Renaud, Lab Chip 4, 114 (2004).

<sup>114</sup>S. Metz, A. Bertsch, D. Bertrand, and P. Renaud, Biosens. Bioelectron. 19, 1309 (2004).

<sup>115</sup>F. Niklaus, P. Enoksson, E. Kälvesten, and G. Stemme, J. Micromech. Microeng. 11, 100 (2001).

<sup>116</sup>T. Sun and H. Morgan, Microfluid. Nanofluid. 8, 423 (2010).

1117 I.-F. Cheng, C.-C. Lin, D.-Y. Lin, and H.-C. Chang, Biomicrofluidics 4, 034104 (2010).

<sup>118</sup>R. Pethig, Biomicrofluidics 4, 022811 (2010).

<sup>119</sup>A. Valero, T. Braschler, N. Demierre, and P. Renaud, Biomicrofluidics 4, 022807 (2010).

<sup>120</sup>J. W. Lee and E. Kjeang, Biomicrofluidics 4, 041301 (2010).

<sup>121</sup>M. Esashi, J. Micromech. Microeng. 18, 073001 (2008).

T. Corman, P. Enoksson, and G. Stemme, Sens. Actuators, A 66, 160 (1998).

<sup>123</sup>J. Chae, J. M. Giachino, and K. Najafi, J. Microelectromech. Syst. 17, 193 (2008).

124C. Iliescu, L. M. Yu, G. L. Xu, and F. E. H. Tay, J. Microelectromech. Syst. 15, 1506 (2006).

<sup>125</sup>C. Iliescu, G. Tresset, and G. L. Xu, Biomicrofluidics 3, 044104 (2009).

<sup>126</sup>C. F. Chen, J. Liu, L. P. Hromada, C. W. Tsao, C. C. Chang, and D. L. DeVoe, Lab Chip 9, 50 (2009).

127 W. van der Wijngaart, H. Andersson, P. Enoksson, K. Noren, and G. Stemme, in Proceedings of IEEE MEMS (IEEE,

Miyazaki, Japan, 2000), p. 674.

128 See http://www.cmscientific.com for the CM Scientific corporate website.

129 See http://www.swagelok.com for the Swagelok corporate website.

<sup>130</sup>See http://www.vici.com for the Valco Instruments Co. Inc., corporate website.

131 V. Saarela, S. Franssila, S. Tuomikoski, S. Marttila, P. Östman, T. Sikanen, T. Kotiaho, and R. Kostiainen, Sens. Actua-

tors B 114, 552 (2005).

<sup>132</sup>T. Pan, A. Baldi, and B. Ziaie, J. Microelectromech. Syst. 15, 267 (2006).

133 A. A. S. Bhagat, P. Jothimuthu, A. Pais, and I. Papautsky, J. Micromech. Microeng. 17, 42 (2007).

134 J. Atencia, G. A. Cooksey, A. Jahn, J. M. Zook, W. N. Vreeland, and L. E. Locascio, Lab Chip 10, 246 (2010).

<sup>135</sup>See http://www.mycorsolutions.com for the CorSolutions corporate website.

```