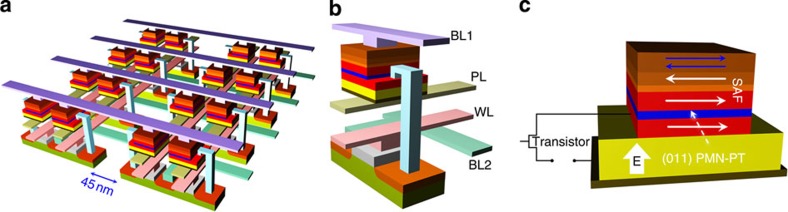

Figure 1. High-density MRAM operating at ultralow voltage at room temperature.

(a) Array design of the electric-field-controlled MRAM device on CMOS platforms. The space between neighbouring cells is taken as 45 nm, which is the typical channel length of its constituent MOS transistor. (b) Architecture of the 1-T(transistor)/1-magnetoresistive (MR) memory unit cell, where the writing voltage is applied between Bitline (BL)2 and Plateline (PL) controlled by Wordline (WL) connecting to the gate of the transistor. (c) Schematic of the basic building block, where a spin valve or magnetic tunnel junction is integrated onto a PMN-PT layer, upon the application of a perpendicular voltage bias controlled by the transistor. (From top to bottom): antiferromagnetic pinning layer, a synthetic antiferromagnetic tri-layer with a pinned layer and a reference layer separated by ultrathin non-magnetic spacer, tunnelling barrier/non-magnetic metallic layer, the magnetic-free layer, ferroelectric layer, and the bottom electrode. The arrows in the MR element denote the magnetization orientations.