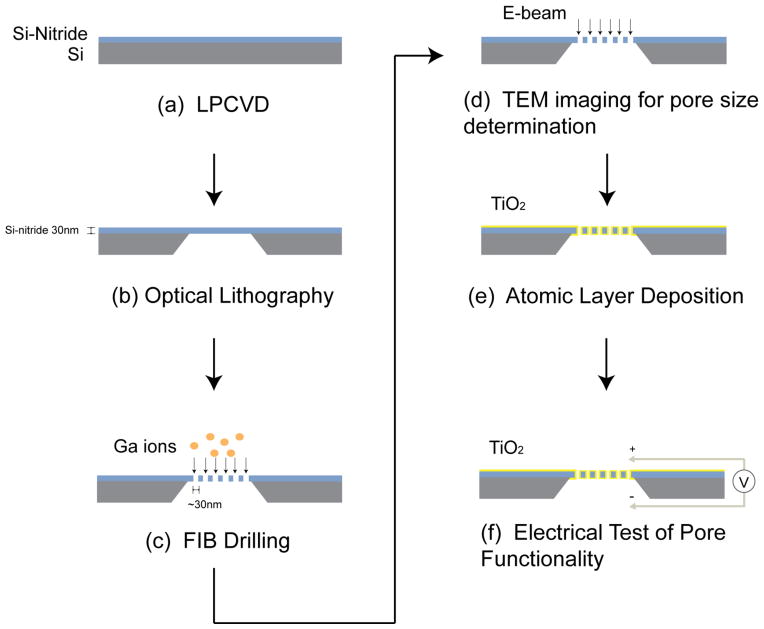

Figure 1.

Schematic of the nanopore array fabrication process. Low Pressure CVD (LPCVD) process was employed to deposit a low-stress nitride layer above the bulk silicon substrate. A free-standing SiN membrane is fabricated using photolithography. Nanopore arrays were drilled through the SiN membrane using FIB milling. The pore size was measured using TEM. Reduction of the nanopore diameters to sub-10 nm range was achieved using ALD.