# **OPEN**

SUBJECT AREAS: ELECTRONIC DEVICES TWO-DIMENSIONAL MATERIALS

2 August 2013

Accepted

24 January 2014

Published

10 February 2014

Received

Correspondence and requests for materials should be addressed to W.J.Y. (yoowj@skku.

# Metal-Semiconductor Barrier Modulation for High Photoresponse in Transition Metal Dichalcogenide Field Effect Transistors

Hua-Min Li, Dae-Yeong Lee, Min Sup Choi, Deshun Qu, Xiaochi Liu, Chang-Ho Ra & Won Jong Yoo

Samsung-SKKU Graphene Center (SSGC), SKKU Advanced Institute of Nano Technology (SAINT), Department of Nano Science and Technology, Sungkyunkwan University, 2066 Seobu-ro, Jangan-gu, Suwon 440-746, Korea.

A gate-controlled metal-semiconductor barrier modulation and its effect on carrier transport were investigated in two-dimensional (2D) transition metal dichalcogenide (TMDC) field effect transistors (FETs). A strong photoresponse was observed in both unipolar  $MoS_2$  and ambipolar  $WSe_2$  FETs (i) at the high drain voltage due to a high electric field along the channel for separating photo-excited charge carriers and (ii) at the certain gate voltage due to the optimized barriers for the collection of photo-excited charge carriers at metal contacts. The effective barrier height between Ti/Au and TMDCs was estimated by a low temperature measurement. An ohmic contact behavior and drain-induced barrier lowering (DIBL) were clearly observed in  $MoS_2$  FET. In contrast, a Schottky-to-ohmic contact transition was observed in  $WSe_2$  FET as the gate voltage increases, due to the change of majority carrier transport from holes to electrons. The gate-dependent barrier modulation effectively controls the carrier transport, demonstrating its great potential in 2D TMDCs for electronic and optoelectronic applications.

ompared to graphene which cannot achieve the low off-state and saturated on-state currents due to its zero bandgap<sup>1-3</sup>, transition metal dichalcogenides (TMDCs) have opened up new opportunities for twodimensional (2D) electronics and optoelectronics such as transistors<sup>4,5</sup>, memories<sup>6,7</sup>, integrated circuits<sup>8,9</sup>, photodetectors<sup>10,11</sup>, and electro-luminescent devices<sup>12</sup> etc., because of their selectable electronic properties ranging from metallic to semiconducting, and tunable bandgaps with layer-dependence<sup>13,14</sup>. Particularly for semiconducting TMDCs such as MoX<sub>2</sub> and WX<sub>2</sub> compounds (X is a chalcogen), their sub-nanometer thickness with sizable bandgaps around 1-2 eV can provide high on/off ratios and more efficient control over switching. The immunity of short-channel effect and ultralow power dissipation which are made possible by using 2D materials can break through the scaling limit for future transistor miniaturization 15,16. For example, MoS<sub>2</sub> as a representative n-type semiconducting TMDC has an indirect bandgap of 1.3 eV in bulk structure but a direct bandgap of 1.8 eV in single-layer form<sup>13</sup>. Owing to the thickness-dependent bandgap modulation, the triple-layer MoS<sub>2</sub> shows a strong photoresponse for red light detection, while the single- and double-layer MoS<sub>2</sub> are preferred for green light detection<sup>11</sup>. The direct bandgap in single-layer MoS<sub>2</sub> also gives rise to photo- and electro-luminescence, posing the potential for novel 2D optoelectronic devices such as light detectors and emitters<sup>12</sup>. Another example, WSe2 with the bandgap of 1.2 eV in bulk structure and 1.7 eV in single-layer form13 has also been studied for transistor<sup>17,18</sup> and photovoltaic applications<sup>13</sup>. Although carrier mobility of MoS<sub>2</sub> and WSe<sub>2</sub> are relatively low, it can be improved significantly by the optimized or chemically doped metal contacts<sup>17,19</sup>, dielectric engineering via high-k materials<sup>4,17</sup>, and formation of an inversion channel<sup>5</sup> etc.

In this work, both few-layer  $MoS_2$  and  $WSe_2$  flakes were applied to the back-gate field effect transistors (FETs) with Ti/Au metallization, and their carrier transport was investigated over a wide range of drain voltage (0 to 5 V) and gate voltage (-50 to 50 V) to demonstrate its strong dependency on bias modulation. To understand the modulation effects more clearly, we investigated the formation of Schottky and ohmic contacts from the  $MoS_2$  and  $WSe_2$  FETs, by measuring the energy barriers of the carriers at the contacts and relating them to the carrier transport and photo-response of these FETs.

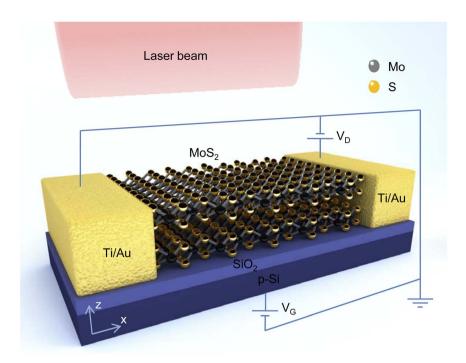

Figure 1 | TMDC FETs under laser illumination. Schematic perspective view and circuit diagram of a TMDC FET under laser illumination with few-layer MoS<sub>2</sub> as channel layer.

#### Results

Thin MoS<sub>2</sub> and WSe<sub>2</sub> flakes are obtained by mechanical exfoliation from the bulk crystals, and transferred to a p-type Si substrate (1.0–10.0  $\Omega$ cm) with 90-nm-thick thermally grown SiO<sub>2</sub> surfaces. The back-gate FET devices are fabricated via electron beam lithography (EBL) with Ti/Au (5 nm/50 nm) electrodes deposited by electron beam evaporation, as shown in Fig. 1. The MoS<sub>2</sub> flake has the thickness of  $\sim$ 3 nm measured by atomic force microscopy (AFM), and its Raman spectrum shows two typical peaks ( $E_{2g}^{-1}$  and  $A_{1g}$ ) with a large separation of 23 cm<sup>-1</sup>. The WSe<sub>2</sub> flake has the thickness of  $\sim$ 9 nm, and only shows a single peak at around 250 cm<sup>-1 20</sup> (Supplementary Information Fig. S1). These suggest the few-layer structure of both MoS<sub>2</sub> and WSe<sub>2</sub> flakes.

The electrical characterization of MoS2 and WSe2 FETs is performed by a semiconductor parameter analyzer in a vacuum condition (10 mTorr) at the room temperature. The optoelectronic performance is analyzed by combining a dot laser (655 nm, 15 mW) illuminating system, where the photocurrent (PC) signal is defined as the difference of drain current  $(I_D)$  in dark and laser illuminating environments at certain drain and gate voltages ( $V_D$ and  $V_G$ ). The  $I_D$ - $V_G$  transfer characteristics of MoS<sub>2</sub> FET illustrate an *n*-type unipolar carrier transport. As a comparison, an asymmetric ambipolar transport with the dominant electron conduction is observed in WSe<sub>2</sub> FET. The trapping-induced hysteresis with voltage shift of 2 and 10 V suggests an equivalent trap density of  $4.79 \times 10^{11}$  and  $2.40 \times 10^{12}$  cm<sup>-2</sup> in MoS<sub>2</sub> and WSe<sub>2</sub> FETs, respectively<sup>21</sup> (Supplementary Information Fig. S2). Before measuring the PC of TMDC FETs, a calibration is performed by measuring the photoresponse of metal and metal/SiO<sub>2</sub> interface. The identical electrical performance in both dark and illuminating environments excludes the photoresponsive contributions of metal and metal/SiO2 interface, and suggests that all the PCs are generated in TMDC FETs.

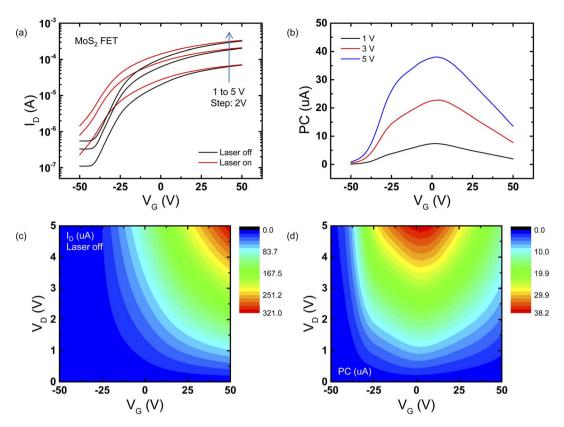

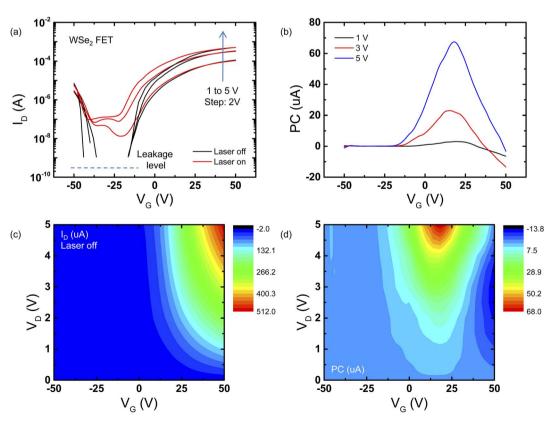

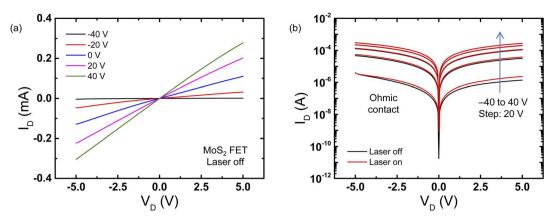

The carrier transport in both MoS<sub>2</sub> and WSe<sub>2</sub> FETs is investigated over a wide range of  $V_D$  (0 to 5 V) and  $V_G$  (-50 to 50 V), as shown in Fig. 2 for MoS<sub>2</sub> FET and in Fig. 3 for WSe<sub>2</sub> FET. In the dark environment, the carrier transport is maximized at the high  $V_G$  (50 V) and  $V_D$  (5 V) levels in both MoS<sub>2</sub> and WSe<sub>2</sub> FETs due to the high carrier

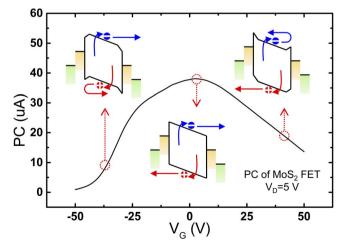

density induced by electrical gating and the high electric field along the channel for carrier drift, respectively. This is consistent with the carrier transport theory in conventional semiconductor FETs. As a comparison, it is interesting to find out that the PC generation in both MoS<sub>2</sub> and WSe<sub>2</sub> FETs is not proportional to the carrier transport in dark environment. The PC peaks under illumination are located at the high  $V_D$  (5 V in both MoS<sub>2</sub> and WSe<sub>2</sub> FETs), owing to the high electric field along the channel for separating the photoexcited charge carriers. However, the PC peaks are located at the different certain  $V_G$  ( $\sim$ 0 V in MoS<sub>2</sub> FET and  $\sim$ 20 V in WSe<sub>2</sub> FET), not at the  $V_G$  of the maximized carrier transport ( $\sim$ 50 V in both MoS<sub>2</sub> and WSe<sub>2</sub> FETs). Therefore, the conventional carrier transport theory is not suitable to explain the transport of photoexcited charge carriers, and thus a new mechanism is required to interpret the gate-dependent photoresponse in TMDCs.

#### **Discussion**

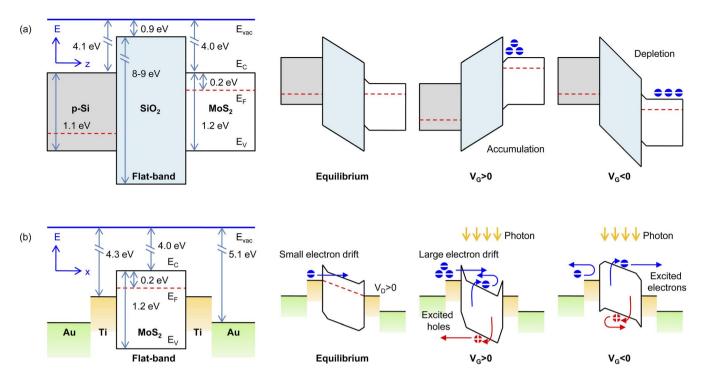

A gate-controlled metal-semiconductor barrier modulation is proposed to interpret the carrier transport of both MoS<sub>2</sub> and WSe<sub>2</sub> under illumination. Here we take the MoS<sub>2</sub> FET as an example due to its unipolar carrier transport which is simpler compared to the case of ambipolar WSe<sub>2</sub> FET. Firstly, the energy band diagrams of MoS<sub>2</sub> FET illustrate the electrical gating effect along the vertical axis for various  $V_G$  conditions, as shown in Fig. 4(a). When  $V_G > 0$ , the electrons are attracted to the interface between MoS2 and SiO2 to form an accumulation layer. When  $V_G < 0$ , the electrons are repelled from the interface to establish a depletion layer. Further increasing the negative  $V_G$  may create an inversion channel which gives rise to the high mobilities<sup>5</sup>. Secondly, the metal-semiconductor barriers at both source and drain ends are modulated capacitively by the gate, as shown in Fig. 4(b). The barriers are induced due to a mismatch between the workfunctions of MoS<sub>2</sub> and Ti, and they can be enlarged or reduced by applying the negative or positive  $V_G$ , respectively. The barrier height ( $\phi_{ms}$ ) at the equilibrium can be theoretically estimated as  $\Phi_M$ – $\chi^{22}$ , where  $\Phi_M$  is the work function of Ti (4.3 eV), and  $\chi$  is the electron affinity of MoS<sub>2</sub> (4.0 eV)<sup>19</sup>. In MoS<sub>2</sub> FET,  $\phi_{ms}$  is estimated as  $0.3\,$  eV, which is in agreement with the theoretical estimation  $^{22,23}$  and experimental results obtained by temperature-dependent electrical

Figure 2 | Photoresponse of transfer characteristic in MoS<sub>2</sub> FET. (a), (b) Transfer characteristic of MoS<sub>2</sub> FET in dark and illuminating environments in forward sweep for various  $V_D$  levels, and the corresponding PCs. (c), (d) Mapping of dark current (laser off) and PC as functions of  $V_D$  and  $V_G$ .

Figure 3 | Photoresponse of transfer characteristic in WSe<sub>2</sub> FET. (a), (b) Transfer characteristic of WSe<sub>2</sub> FET in dark and illuminating environments in forward sweep for various  $V_D$  levels, and the corresponding PCs. (c), (d) Mapping of dark current (laser off) and PC as functions of  $V_D$  and  $V_G$ .

Figure 4 | Energy band diagrams of MoS<sub>2</sub> FET. The energy band diagrams along (a) the vertical axis (z) and (b) the horizontal axis (x) illustrate various gating conditions, including flat-band, equilibrium ( $V_G = 0$ ), accumulation ( $V_G > 0$ ) and depletion ( $V_G < 0$ ). The blue solid line and red dash line denote the vacuum and Fermi levels, respectively. The blue and red arrows indicate the transport of electrons and holes.

measurements<sup>8,19,24,25</sup> previously. Thirdly, the carrier transports in both dark and illuminating environments are strongly affected by the gate-dependent barrier modulation. For the electron drift along the channel driven by a positive  $V_D$ , the barriers are reduced with increasing  $V_G$ , allowing the electrons to transport through by tunneling effect or thermionic emission in the dark environment. As a comparison, for the photon-excited charge carriers generated within the channel under illumination, the barriers only allow the electron collection at the drain end, but suppress the hole collection at the source end when  $V_G < 0$ , and vice versa when  $V_G > 0$ . Therefore, the PC generation is still relatively small at the high positive and negative  $V_G$  levels due to the inefficient carrier collection. However, there should be an optimized  $V_G$  condition where the barriers for both electron and hole collection are minimized at the source and drain ends concurrently, contributing to a peak PC generation. This gatecontrolled barrier modulation can thoroughly interpret the gatedependent photoresponse of MoS<sub>2</sub> FET, as shown in Fig. 5. Similarly, it can also be applied to WSe2 FET due to the analogous energy bandgap. Finally, the channel current under illumination, which is the sum of both dark current and PC, shows the gate dependence following a combined barrier modulation for both electron drift and photo-excited charge carriers.

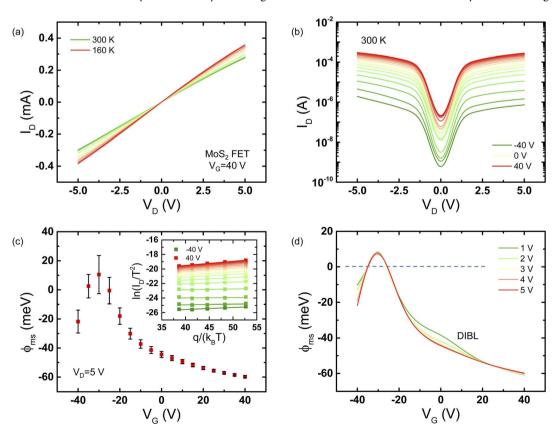

To quantitatively analyze the barrier modulation, the effective value of  $(\phi_{ms})$  between metal and TMDC is obtained by testing the temperature dependence of channel current<sup>25,26</sup>. A typical ohmic contact behavior in the  $I_D$ - $V_D$  output characteristics of MoS $_2$  FET and its photoresponse are observed at various  $V_G$  levels, as shown in Fig. 6. For the carrier transport through a metal-semiconductor barrier, the tunneling effect dominates when the semiconductor is highly doped, whereas the thermionic emission dominates when the semiconductor is slightly or moderately doped. Since the MoS $_2$  is intrinsic in this work, the current-voltage relation is determined by thermionic emission as  $^{26}$

$$I_D = AA^*T^2 \exp\left(\frac{-\phi_{ms}}{k_BT}\right) \left[\exp\left(\frac{-qV_D}{k_BT}\right) - 1\right]$$

(1)

where A is the area of the contact junction,  $A^*$  is the effective Richardson constant, q is the electronic charge,  $k_B$  is the Boltzmann constant, and T is the temperature. Considering the electron transport from the source to the drain ends, a back-to-back metal-semiconductor-metal contact is formed, and the carrier transport is mainly affected by the contact condition at the drain end due to the applied  $V_D$ . Under a high  $V_D$ , the contact at the drain end is reversely biased  $[\exp(-qV_D/k_BT) \ll 1]$ , and  $I_D$  becomes proportional to  $T^2\exp(-\phi_{ms}/k_BT)$ . A linear relation between  $\ln(I_D/T^2)$  and  $q/k_BT$  can be plotted for various  $V_G$  levels, and the gate-dependent  $\phi_{ms}$  for a given  $V_D$  is estimated from the slope of each curve, as shown in Fig. 7.  $\phi_{ms}$  has a very low value

Figure 5 | Gate-dependent barrier modulation in MoS<sub>2</sub> FET. The barriers at both source and drain ends can be minimized at certain  $V_G$ , which promote the collection of photo-excited charge carriers and contribute to a PC peak. The PC generation as a function of  $V_G$  in WSe<sub>2</sub> FET can also be interpreted analogously.

Figure 6 | Ohmic contact and its photoresponse in MoS<sub>2</sub> FET. (a), (b) Output characteristic of MoS<sub>2</sub> FET for various  $V_G$  levels in linear scale and its photoresponse in logarithmic scale, suggesting an ohmic contact behavior.

on the order of 10 meV, which is in agreement with the presence of ohmic contact.  $\phi_{ms}$  also shows a reduction as  $V_G$  increases, being consistent with the barrier modulation theory. Moreover, a reduction of  $\phi_{ms}$  with increasing  $V_D$  is clearly observed near zero gate voltage, suggesting a drain-induced barrier lowering (DIBL) effect in MoS<sub>2</sub> FET. Besides, it is noted that  $\phi_{ms}$  is reduced at very high negative  $V_G$ . This may be induced by the increased minority carrier density during the formation of inversion layer.

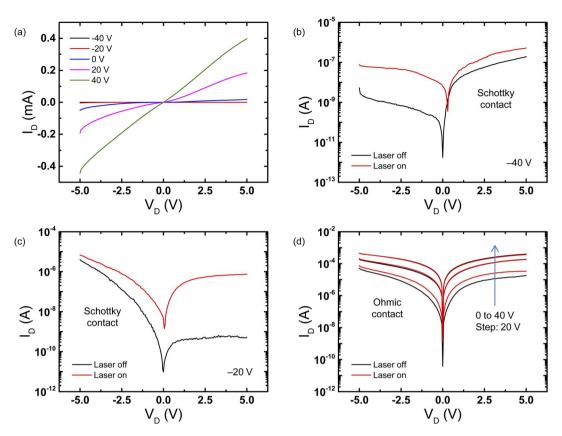

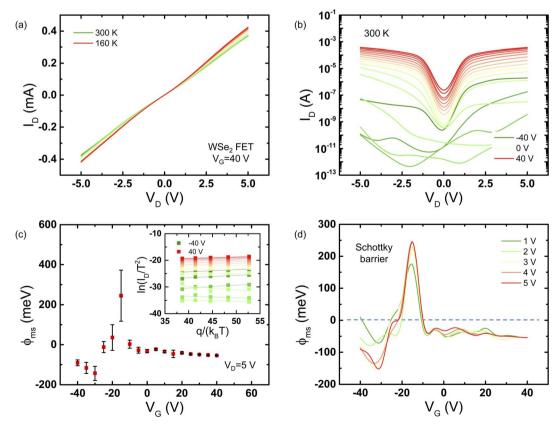

For the WSe<sub>2</sub> FET, a transition from Schottky to ohmic contact is observed, as shown in Fig. 8. The current-voltage relation shows the Schottky contact behavior with opposite polarities at  $V_G$  of -40 and -20 V, but then shows the ohmic contact behavior as  $V_G$  increases from 0 V to 40 V. Considering the ambipolar transport of WSe<sub>2</sub>, this Schottky-to-ohmic contact transition may be induced by the change

of majority carrier transport from holes at negative  $V_G$  to electrons at positive  $V_G$  (see Fig. 3(a)). The experimental value of  $\phi_{ms}$  is obtained as a function of  $V_G$ , as shown in Fig. 9.  $\phi_{ms}$  shows a dip near  $-40~\rm V$  and a peak near  $-20~\rm V$ , indicating the Schottky contact with opposite polarities. As  $V_G$  increases further, the value of  $\phi_{ms}$  is reduced from the order of 100 to 10 meV, suggesting a transition from Schottky to ohmic contact.

In conclusion, the bias-controlled barrier modulation in TMDC FETs and its effect on carrier transport were investigated over a wide range of gate and drain voltages. Being disproportionate to the conventional carrier transport in dark environment, a strong photoresponse was observed at the certain gate and drain voltages due to the change in barrier heights between metal and TMDC materials which resulted in ohmic contact or Schottky contact. The gate-dependent

Figure 7 | Extraction of barrier height in MoS<sub>2</sub> FET. (a), (b) Output characteristic of MoS<sub>2</sub> FET for various temperatures (160 to 300 K with a step of 20 K) and  $V_G$  (-40 to 40 V with a step of 5 V) levels. (c), (d) Effective barrier height as a function of  $V_G$  for various  $V_D$  levels. Inset of (c): Temperature-dependent current characteristics and their corresponding linear fit for various  $V_G$  levels at  $V_D$  of 5 V.

Figure 8 | A Schottky-to-ohmic contact transition and its photoresponse in WSe<sub>2</sub> FET. (a) Output characteristic of WSe<sub>2</sub> FET for various  $V_G$  levels in linear scale. (b–d) Photoresponse of output characteristic in logarithmic scale indicates a transition from Schottky contact to ohmic contact as  $V_G$  increases.

Figure 9 | Extraction of barrier height in WSe<sub>2</sub> FET. (a), (b) Output characteristic of WSe<sub>2</sub> FET for various temperatures (160 to 300 K with a step of 20 K) and  $V_G$  (-40 to 40 V with a step of 5 V) levels. (c), (d) Effective barrier height as a function of  $V_G$  for various  $V_D$  levels. Inset of (c): Temperature-dependent current characteristics and their corresponding linear fit for various  $V_G$  levels at  $V_D$  of 5 V.

barrier modulation effectively controlled the carrier transport in  $MoS_2$  and  $WSe_2$ .

## **Methods**

**Fabrication of TMDC FET devices.** Both  $MoS_2$  and  $WSe_2$  thin flakes were mechanically exfoliated from bulk crystals by using scotch tapes. Before the transfer procedure, the silicon wafer was pre-cleaned by sonication in acetone, isopropyl alcohol, and deionized water, followed by drying in nitrogen flow and heating on hot plate to remove the moisture. Electrodes were patterned by standard EBL procedure. 5-nm-thick Ti and 50-nm-thick Au were deposited by electron beam evaporation, followed by a post-annealing in  $N_2$  environment at  $300^{\circ}\text{C}$  for 1 hour to improve the metal contact.

- 1. Schwierz, F. Graphene transistors. Nature Nanotech. 5, 487-496 (2010).

- Bonaccorso, F., Sun, Z., Hasan, T. & Ferrari, A. C. Graphene photonics and optoelectronics. *Nature Photo.* 4, 611–622 (2010).

- Castro Neto, A. H. & Novoselov, K. New directions in science and technology: two-dimensional crystals. Rep. Prog. Phys. 74, 082501 (2011).

- Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-layer MoS<sub>2</sub> transistors. *Nature Nanotech.* 6, 147–150 (2011).

- Kim, S. et al. High-mobility and low power thin-film transistors based on multilayer MoS<sub>2</sub> crystals. Nature Commun. 3, 1011 (2012).

- Choi, M. S. et al. Controlled charge trapping by molybdenum disulphide and graphene in ultrathin heterostructured memory devices. Nature Commun. 4, 1624 (2013)

- Bertolazzi, S., Krasnozhon, D. & Kis, A. Nonvolatile memory cells based on MoS<sub>2</sub>/ graphene heterostructures. ACS Nano 7, 3246–3252 (2013).

- Yu, W. J. et al. Vertically stacked multi-heterostructures of layered materials for logic transistors and complementary inverters. Nature Mater. 12, 246–252 (2013).

- Wang, H. et al. Integrated circuits based on bilayer MoS<sub>2</sub> transistors. Nano Lett. 12, 4674–4680 (2012).

- Lopez-Sanchez, O., Lembke, D., Kayci, M., Radenovic, A. & Kis, A. Ultrasensitive photodetector based on monolayer MoS<sub>2</sub>. Nature Nanotech. 8, 497–501 (2013).

- Lee, H. S. et al. MoS<sub>2</sub> nanosheet phototransistors with thickness-modulated optical energy gap. Nano Lett. 12, 3695–3700 (2012).

- Sundaram, R. S. et al. Electroluminescence in single layer MoS<sub>2</sub>. Nano Lett. 13, 1416–1421 (2013).

- Wang, Q. H., Kalantar-Zadeh, K., Kis, A., Coleman, J. N. & Strano, M. S. Electronics and optoelectronics of two-dimensional transition metal dichalcogenides. *Nature Nanotech.* 7, 699–712 (2012).

- Chhowalla, M. et al. The chemistry of two-dimensional layered transition metal Dichalcogenide nanosheets. Nature Chem. 5, 263–275 (2013).

- Liu, H., Neal, A. T. & Ye, P. D. Channel length scaling of MoS<sub>2</sub> MOSFETs. ACS Nano 6, 8563–8569 (2012).

- Liu, H., Gu, J. & Ye, P. D. MoS<sub>2</sub> nanoribbon transistors: transition from depletion mode to enhancement mode by channel-width trimming. *IEEE Electron Device Lett.* 33, 1273–1275 (2012).

- Fang, H. et al. High-performance single layered WSe<sub>2</sub> p-FETs with chemically doped contacts. Nano Lett. 12, 3788–3792 (2012).

- Liu, W. et al. Role of metal contacts in designing high-performance monolayer ntype WSe<sub>2</sub> field effect transistors. Nano Lett. 13, 1983–1990 (2013).

- Das, S., Chen, H.-Y., Penumatcha, A. V. & Appenzeller, J. High performance multilayer MoS<sub>2</sub> transistors with scandium contacts. *Nano Lett.* 13, 100–105 (2013).

- Tonndorf, P. et al. Photoluminescence emission and Raman response of monolayer MoS<sub>2</sub>, MoSe<sub>2</sub>, and WSe<sub>2</sub>. Optics Exp. 21, 4908–4916 (2013).

- 21. Wang, H., Wu, Y., Cong, C., Shang, J. & Yu, T. Hysteresis of electronic transport in graphene transistors. *ACS Nano* 4, 7221–7228 (2010).

- Choi, W. et al. High-detectivity multilayer MoS<sub>2</sub> phototransistors with spectral response from ultraviolet to infrared. Adv. Mater. 24, 5832–5836 (2012).

- Lee, K. et al. Electrical characteristics of molybdenum disulfide flakes produced by liquid exfoliation. Adv. Mater. 23, 4178–4182 (2011).

- 24. Chen, J.-R. et al. Control of Schottky barriers in single layer MoS<sub>2</sub> transistors with ferromagnetic contacts. Nano Lett. 13, 3106–3110 (2013).

- Yang, H. et al. Graphene barristor, a triode device with a gate-controlled Schottky barrier. Science 336, 1140–1143 (2012).

- Neamen, D. A. Semiconductor physics and devices: basic principles. 3<sup>rd</sup> ed. McGraw-Hill (2003).

#### **Acknowledgments**

This work is supported by the Basic Science Research Program through the National Research Foundation of Korea (NRF) (2009-0083540, 2011-0010274, 2013-015516), and by the Global Frontier R&D Program (2013-073298) on Center for Hybrid Interface Materials (HIM) funded by the Ministry of Science, ICT & Future Planning.

### **Author contributions**

H.M.L. and W.J.Y. conceived the research project, supervised the experiment and wrote the paper. H.M.L., D.Y.L. and M.S.C. performed device fabrication. H.M.L. performed electrical and optoelectronic characterization. D.Q. performed AFM analysis. X.L. performed theoretical simulation. C.H.R. performed Raman spectrum analysis.

#### Additional information

${\bf Supplementary\ information\ accompanies\ this\ paper\ at\ http://www.nature.com/scientificreports}$

Competing financial interests: The authors declare no competing financial interests.

How to cite this article: Li, H.-M. *et al.* Metal-Semiconductor Barrier Modulation for High Photoresponse in Transition Metal Dichalcogenide Field Effect Transistors. *Sci. Rep.* 4, 4041; DOI:10.1038/srep04041 (2014).

This work is licensed under a Creative Commons Attribution-NonCommercial-NoDerivs 3.0 Unported license. To view a copy of this license, visit http://creativecommons.org/licenses/by-nc-nd/3.0