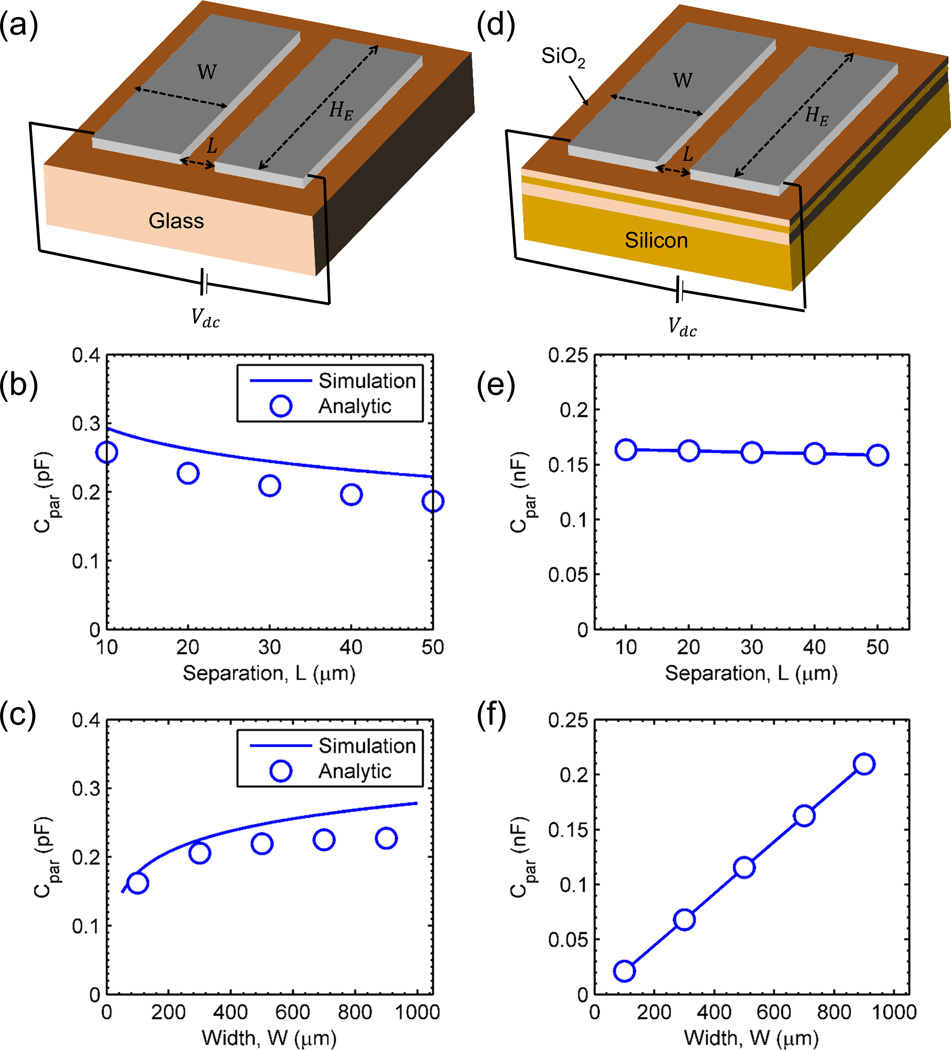

Fig. 6.

Simulation of parasitic capacitance for two different substrates. Geometry used for the simulation for glass substrate (a) and SOI substrate (d). Variation of parasitic capacitance as a function of (b), (e) electrode separation and (c), (f) electrode width for glass and SOI substrate respectively.