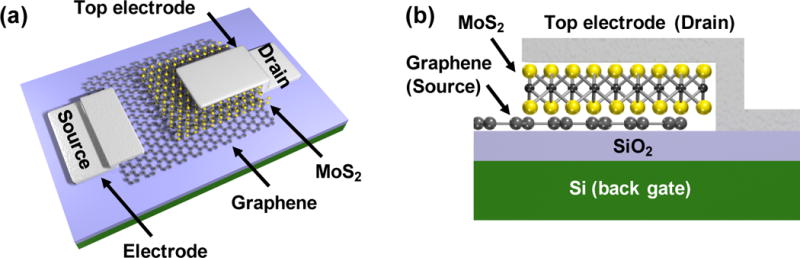

Figure 1. Schematic illustration of the vertically stacked graphene-MoS2-metal field-effect transistors.

a, A schematic illustration of the three-dimensional view of the device layout. b, A schematic illustration of the cross-sectional view of the device, with the graphene and top metal thin film functioning as the source and drain electrodes, the MoS2 layer as the vertically stacked semiconducting channel and its thickness defines the channel length. Silicon back gate is used with 300-nm SiO2 dielectric layer.