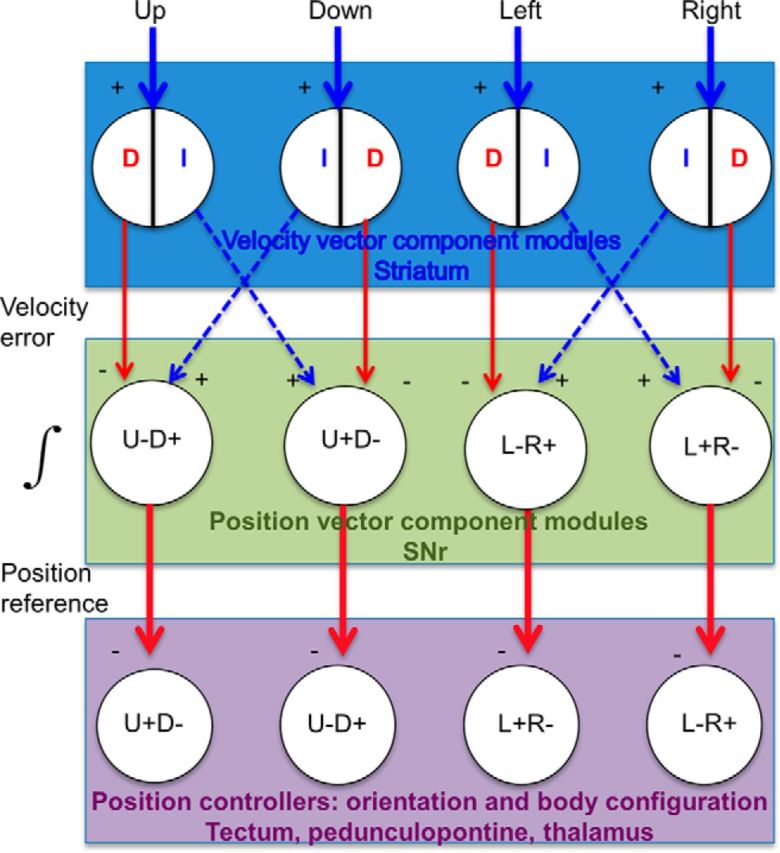

Figure 14.

Hypothetical BG circuit. SNr neurons receive projections from the striatum and external globus pallidus, via the direct (D, striatonigral) and indirect (I, striatopallidal) pathways. Although these projections are GABAergic, the net effect on the SNr can be either inhibitory (−) or excitatory (disinhibitory, +). Both types of signals, corresponding to a velocity error signal from the striatum, enter the SNr integrator, which is assumed to be leaky. Of course, direct and indirect pathways are not the only possible neural implementation of the proposed circuit. The key component is a phase splitter that generates opponent position reference signals from the SNr to the relevant downstream position controllers. Similar to reciprocal inhibition in the spinal cord, the proposed circuit generates opponent outputs for movement in any direction. For example, for upward movement, the indirect pathway neurons in the “Up” module increase the firing rate of SNr “Up+” neurons, whereas the direct pathway from the same module decreases the firing rate of SNr “Down+” neurons. The coordinated opponent outputs from this module generate movement in the desired direction. The rate of SNr output reflects the time integral of the striatal output. The striatum, especially the sensorimotor region, is hypothesized to contain at least four different modules, each responsible for movement in a specific direction. Because z-axis motion has not been measured, only four directions are illustrated here. Two of the four vector components are associated with any movement (e.g., upward and rightward), as movements usually have both horizontal and vertical components. The total output (number of spikes) from a particular striatal module represents the magnitude of the isolated position vector component, and the firing rate represents velocity (Kim et al., 2014). Using the outputs from different vector component modules, this circuit can perform vector addition to generate the resultant vector.