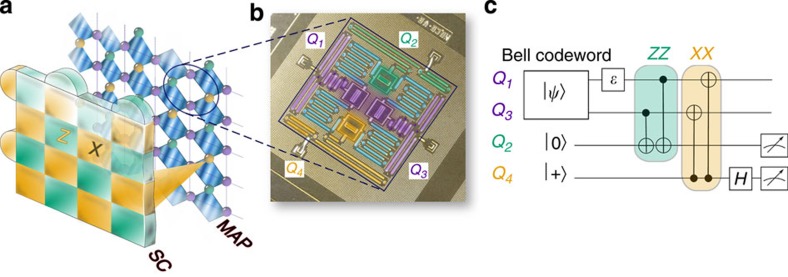

Figure 1. Surface code implementation and error detection quantum circuit.

(a) Cartoon schematic of SC consisting of alternating square tiles of X- (yellow) and Z- (green) plaquettes for detecting phase-flip (Z) and bit-flip (X) errors, respectively. Semi-circular pieces reflect parity checks at the boundaries of the lattice. These plaquette tiles can be mapped onto a lattice of physical superconducting qubits with appropriate nearest-neighbour interconnectivity, as shown in the layer labelled MAP. Here there are code qubits (purple spheres), X-syndrome qubits (yellow) for phase parity detection of surrounding code qubits, and Z-syndrome qubits (green) for bit parity detection of surrounding code qubits. The physical connectivity for superconducting qubits can be realised via coupling every qubit to two quantum bus resonators, shown as wavy blue diamonds in the MAP. The device studied in this work (false-colored optical micrograph in b) embodies two half-plaquettes of the SC as circled in a, and allows for independent and simultaneous detection of X and Z errors on two-code qubits, shaded purple in b and labelled Q1 and Q3. (c) The circuit to implement the half-plaquette operations encodes the bit (ZZ) and phase (XX) parities of the two-code qubits' Bell state  onto the respective syndrome qubits, Q2 (green) and Q4 (yellow). Arbitrary errors ɛ are intentionally introduced on the code qubit Q1 and detected from the correlated measurement of the syndrome qubits. Q2 (Q4) is initialized to

onto the respective syndrome qubits, Q2 (green) and Q4 (yellow). Arbitrary errors ɛ are intentionally introduced on the code qubit Q1 and detected from the correlated measurement of the syndrome qubits. Q2 (Q4) is initialized to  . A Hadamard operation, H, is applied to Q4 before measurement.

. A Hadamard operation, H, is applied to Q4 before measurement.