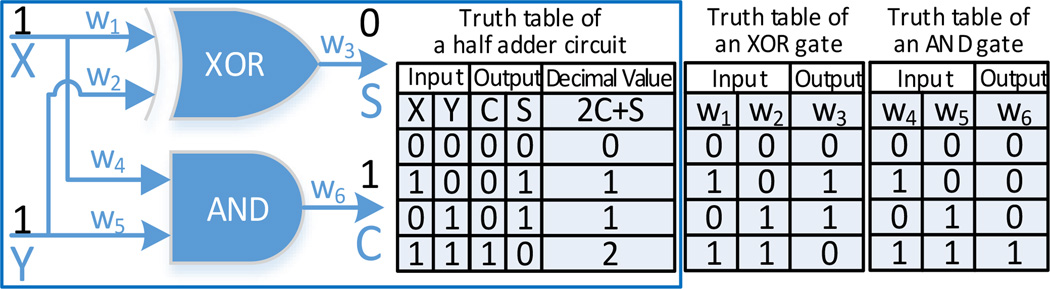

Fig. 3.

An example of a half adder circuit in implementing function fha(x, y) = x + y with x, y ∈ {0, 1}, which includes an XOR gate and an AND gate. The half adder has two single binary inputs x and y and two outputs, i.e., sum (S) and carry (C), where the decimal output can be represented as fha(x, y) = 2C + S. Each logic gate (e.g., XOR or AND gate) has three wires, which correspond to two binary inputs (e.g., W1 and W2 in the XOR gate) and one binary output (e.g., W3 in the XOR gate). The truth tables of the half adder circuit, XOR and AND gates have been shown as references.