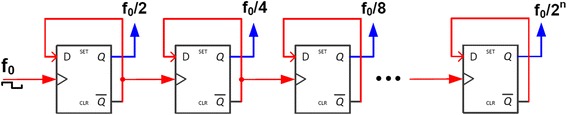

Fig. 5.

Block diagram of the frequency divider design. Each D-flip-flop is used to realize a “divide-by-2” circuit by connecting the output to its own input D. For example, clock input with a frequency of f0 is fed into the first flip-flops to generate f0/2. This f0/2 is again used to clock the second flip flop and generate f0/4. The sequence can be extended indefinitely. If implemented on-chip, both circuit area and power consumption will be very small and thus can be powered by a miniature battery.