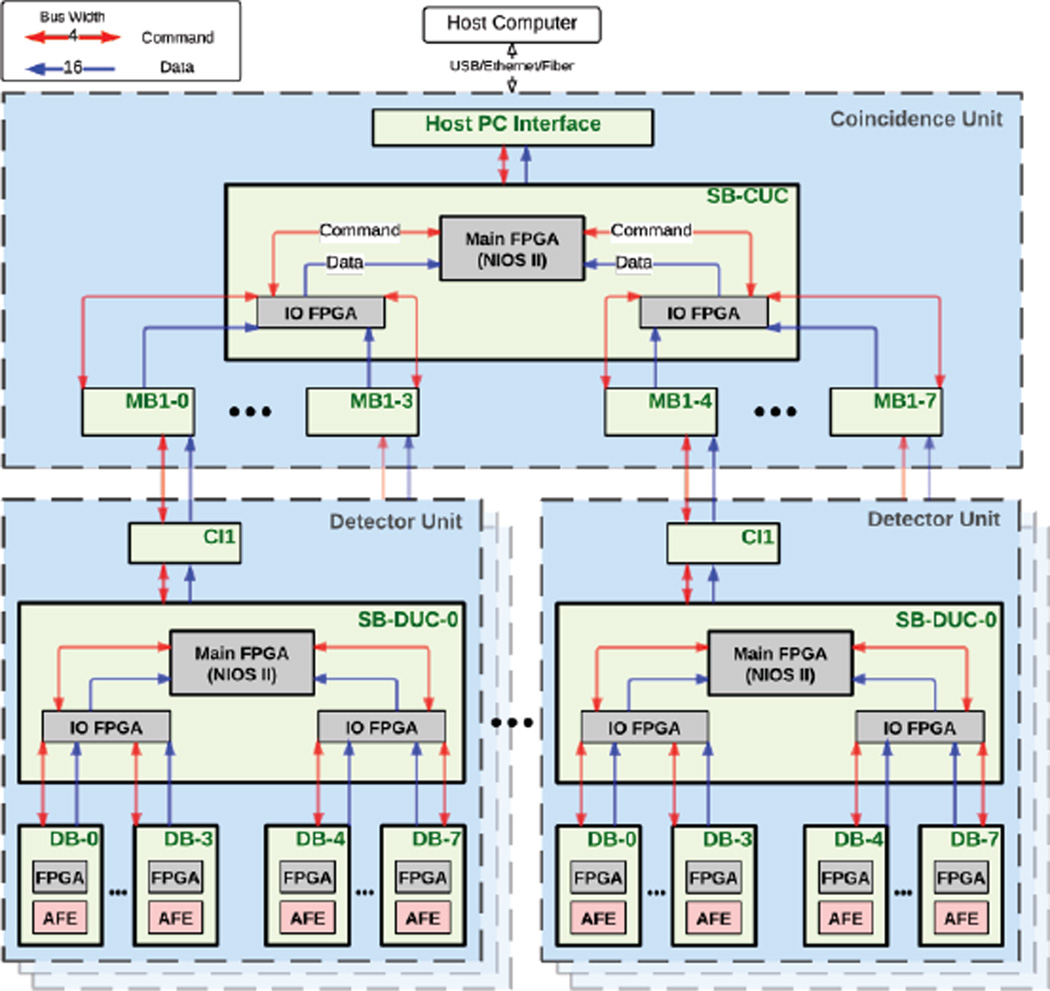

Fig. 5.

Simplified Standard System architecture. An analog detector signal is passed through the analog front end (AFE) for filtering, timestamping, and digitization. Then it is processed using real-time algorithms on the DB’s FPGA and handed over to an IO FPGA for multiplexing. Finally it is given to the main FPGA for correlation and combination. A DU packs the formatted data and passes it to its parent chassis.