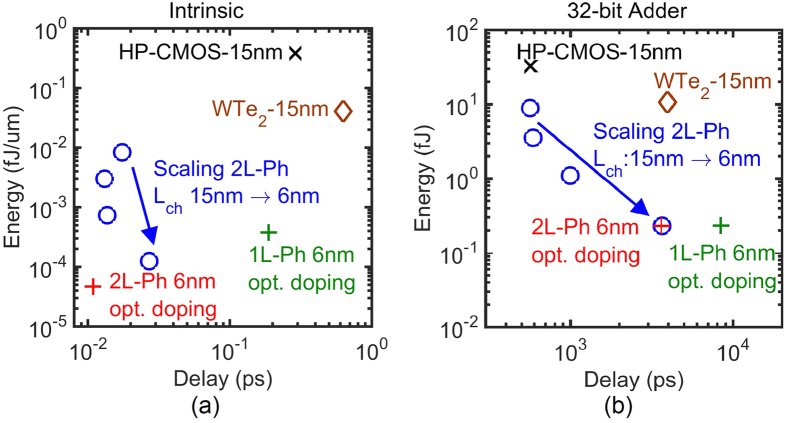

Figure 5. The energy delay (ED) of 2L-phosphorene at different scaling nodes calculated for (a) intrinsic device and (b) 32-bit adder circuit.

Phosphorene provides lower energy delay product (EDP) than WTe2 and CMOS. Although, scaling down significantly improves the intrinsic EDP, the improvement in the adder EDP is less due to the dominance of parasitics in smaller dimensions. For the 6 nm node, optimized 2L-phosphorene with asymmetric doping provides the lowest possible intrinsic EDP, such improvements are not felt in the adder EDP due to the dominance of parasitics.