Article

# I-V and C-V Characterization of a High-Responsivity Graphene/Silicon Photodiode with Embedded MOS Capacitor

Giuseppe Luongo <sup>1,2</sup> , Filippo Giubileo <sup>2</sup> , Luca Genovese <sup>1</sup>, Laura Iemmo <sup>1</sup>, Nadia Martucciello <sup>2</sup> and Antonio Di Bartolomeo <sup>1,2,\*</sup>

- Dipartimento di Fisica "E. R. Caianiello", Università di Salerno, via Giovanni Paolo II 132, 84084 Fisciano, Italy; giluongo@unisa.it (G.L.); genoveseluca89@gmail.com (L.G.); liemmo@unisa.it (L.I.)

- <sup>2</sup> CNR-SPIN Salerno, via Giovanni Paolo II 132, 84084 Fisciano, Italy; filippo.giubileo@spin.cnr.it (F.G.); nadia.martucciello@spin.cnr.it (N.M.)

- \* Correspondence: adibartolomeo@unisa.it; Tel.: +39-089-969-189

Received: 9 June 2017; Accepted: 22 June 2017; Published: 27 June 2017

**Abstract:** We study the effect of temperature and light on the I-V and C-V characteristics of a graphene/silicon Schottky diode. The device exhibits a reverse-bias photocurrent exceeding the forward current and achieves a photoresponsivity as high as 2.5 A/W. We show that the enhanced photocurrent is due to photo-generated carriers injected in the graphene/Si junction from the parasitic graphene/SiO<sub>2</sub>/Si capacitor connected in parallel to the diode. The same mechanism can occur with thermally generated carriers, which contribute to the high leakage current often observed in graphene/Si junctions.

Keywords: graphene; Schottky barrier; MOS capacitor; photodiode; photocurrent

## 1. Introduction

Graphene is a 2D structure possessing high thermal conductivity [1], high mobility and electrical conductivity [2], maximum surface to volume ratio, low contact resistance [3–5] and easy down-scaling [6]. All these properties make it suitable for electronics devices [7], chemical sensors, photodetectors [8] and solar cells [9]. The graphene/silicon (Gr/Si) junction is one of the simplest devices in a hybrid graphene-semiconductor technology. It offers the opportunity to study the physical phenomena that occur at the interface between a gapless 2D and a semiconducting 3D material. The underlying physics in Gr/Si junctions is not yet fully understood. These devices can behave as Schottky diodes and exhibit a rectifying behavior, with current-voltage (I-V) forward characteristics described by the thermionic theory and bias-dependent reverse saturation current. The growing reverse-bias current has been explained by the modulation of the Schottky barrier caused by the low density of states of graphene [10].

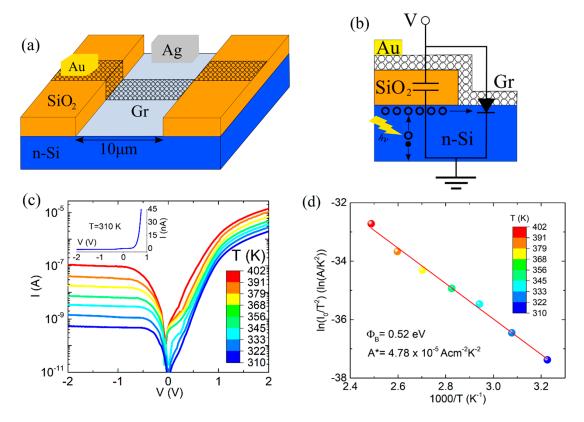

In this paper, we characterize a planar Gr/Si junction where part of the graphene is in contact with the n-type silicon, while the remaining part extends over the  $SiO_2$  insulating layer, forming a metal-oxide-semiconductor (MOS) capacitor (Figure 1a). We demonstrate that the  $Gr/SiO_2/Si$  MOS capacitor (Figure 1b) is able to affect the electrical features of the Gr/Si junction and contributes to its high optical responsivity.

*Nanomaterials* **2017**, *7*, 158

Figure 1. (a) Schematic view of the device and (b) equivalent circuit; (c) I-V characteristic of the Gr/Si junction for decreasing temperature from 400 K to 300 K. The temperature values listed in the figure are measured with an error of  $\pm 1$  K. The inset shows the I-V characteristic at 310 K in linear scale; (d) Richardson plot of  $\ln \left( I_0/T^2 \right)$  versus  $10^3/T$ .

#### 2. Results and Discussion

Figure 1c shows the I-V characteristics of the device in semi-logarithmic scale, measured in dark and in the 300-400 K temperature range. The device exhibits a rectifying behavior, with a rectification ratio of up to  $10^3$ , saturated reverse current, turn-on voltage of  $\sim 0.5$  V at 1 nA current and 310 K, and forward current exponentially growing until reaching the series-resistance  $R_{\rm S}$  limited region, characterized by a downward curvature.

The I-V behavior can be expressed by the thermionic emission model [10]:

$$I = I_0 \left[ \exp\left(\frac{qV}{nkT}\right) - 1 \right] \tag{1}$$

where n is the ideality factor, q is the electron charge, T the temperature, and k the Boltzmann constant.  $I_0$  is the reverse saturation current (leakage) which is expressed as

$$I_0 = AA^*T^2 \exp\left(-\frac{\Phi_{b0}}{kT}\right) \tag{2}$$

with  $A=4\times 10^{-4}~{\rm cm}^2$  the active device area,  $A^*=112~{\rm Acm}^{-2}{\rm K}^{-2}$  the theoretical effective Richardson constant for n-Si and  $\Phi_{b0}$  the Schottky barrier height. The ideality factor accounts for mechanisms other than pure thermionic injection as well as for defects or unwanted insulating layers, inadvertently introduced at the Gr/Si interface during the fabrication process. Defects and insulating patches can introduce Schottky barrier inhomogeneity.

*Nanomaterials* **2017**, *7*, 158

We extracted the Schottky barrier height and the effective Richardson constant from the Richardson plot shown in Figure 1d. Rewriting Equation (2) in the form:

$$\ln\left(\frac{I_0}{T^2}\right) = \ln(AA^*) - \frac{\Phi_{b0}}{k} \frac{1}{T} \tag{3}$$

$\Phi_{b0}$  and  $A^*$  can be evaluated from the slope and the intercept of the plot of  $\ln(I_0T^2)$  vs.  $10^3/T$ , respectively. The resulting  $A^*=4.78\times 10^{-5}~A{\rm cm}^{-2}~{\rm K}^{-2}$  is significantly lower than the theoretical value in metal-semiconductor junctions, and  $\Phi_{b0}=0.52~{\rm eV}$ . The origin of a lower effective Richardson constant, which has often been a matter of discussion [11,12], can be attributed to the presence of an insulating layer at Gr/Si interface, such as native oxide. Rewriting Equation (2) as:

$$I_0 = AA^*T^2 \exp\left(-\chi^{1/2}\delta\right) \exp\left(-\frac{\Phi_{b0}}{kT}\right) \tag{4}$$

with the introduction of a tunneling attenuation factor  $\exp\left(-\chi^{\frac{1}{2}} \delta\right)$ , where  $\chi$  (expressed in eV) is the mean barrier height and  $\delta$  (expressed in Å) is the thickness of the insulating layer (a dimensional constant of  $\left[2(2m^*)\hbar^2\right]^{\frac{1}{2}}\approx 1.01~\text{eV}^{\frac{1}{2}}~\text{Å}^{-1}$  is commonly omitted),  $m^*$  is the effective electron mass,  $\hbar$  is the reduced Planck constant, the Richardson constant can be redefined as

$$A^{**} = A^* \exp\left(-\chi^{1/2}\delta\right) \tag{5}$$

Assuming that  $A^*=112~A\text{cm}^{-2}~K^{-2}$  and  $\chi\approx 3~\text{eV}$  for a SiO<sub>2</sub> interfacial layer,  $A^{**}=4.78\times 10^{-5}~A\text{cm}^{-2}~K^{-2}$  and  $\delta\sim 8.5$  Å are extracted from the intercept of the Richardson plot. The interface insulating layer, which has been confirmed by X-ray photoelectron spectroscopy measurements (not reported, here, for brevity), reduces the minority-carrier tunneling current without affecting the majority carrier current, which is from diffusion, and raises the majority injection efficiency [13,14].

The series resistance  $R_S$  can be evaluated using Cheung's method [15]. Taking into account the voltage drop on the series resistance,  $R_SI$ , Equation (1) becomes

$$I = I_0 \left[ \exp\left(\frac{q(V - R_S I)}{nkT}\right) - 1 \right] \tag{6}$$

From Equation (6), when -1 can be neglected, two equations can be derived, both yielding  $R_S$ :

$$\frac{\mathrm{d}V}{\mathrm{d}\ln(I)} = IR_{\mathrm{S}} + n\left(\frac{\mathrm{k}T}{\mathrm{q}}\right) \tag{7}$$

and

$$H(I) = V - n\left(\frac{kT}{q}\right) \ln\left(\frac{I}{AA^{**}T^2}\right) \tag{8}$$

where H(I) is defined as

$$H(I) = IR_{\rm S} + n\Phi_{\rm b0} \tag{9}$$

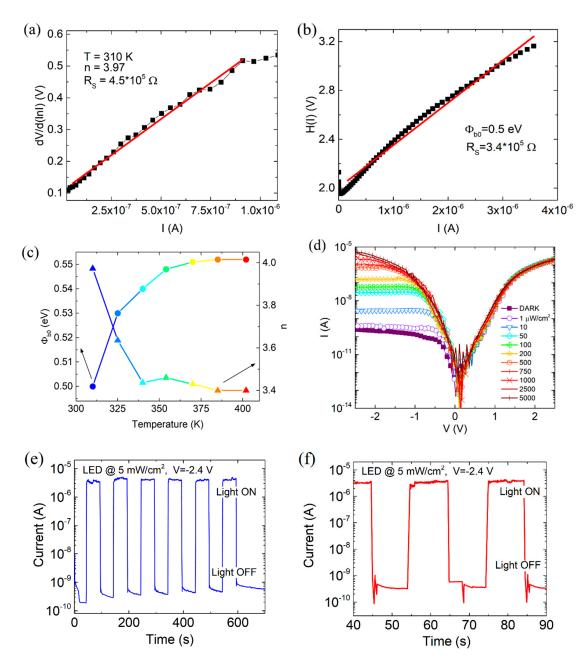

Figure 2a plots  $dV/d \ln I$  vs. I at 310 K. In the  $R_S$  limited region, Equation (7) predicts a straight line with slope and intercept that can be used to extract the series resistance  $R_S$  and the ideality factor n, respectively.

Once the ideality factor is determined, the right-hand side of Equation (8) can be computed from the current and bias voltage measured in the  $R_{\rm S}$  limited region. According to Equation (9), the  $H({\rm I})$  vs. I plot (Figure 2b), is a straight line whose slope and intercept are the series resistance and the product  $n\Phi_{\rm b0}$ , respectively. Averaging the values extracted from Equations (7)–(9),  $R_{\rm S}\sim 400~{\rm k}\Omega$ , while from Equation (9),  $\Phi_{\rm b0}\approx 0.52~{\rm eV}$ , a value in agreement with the barrier height previously estimated with the Richardson method.

Nanomaterials 2017, 7, 158 4 of 8

**Figure 2.** Cheung's plot of (a) dV/dln(I) versus I and (b) H(I) vs. I. (c) Temperature dependence of ideality factor and barrier height. (d) Room-temperature I-V characteristics of the Gr/Si junction under different illumination levels from a white LED array. (e,f) Dynamic measurement of the photocurrent at reverse bias V = -2.4 V and light intensity of 5 mW/cm², showing a time response with rise and fall time of  $\sim 0.5$  s, corresponding to the time resolution of the source-measurement unit.

Figure 2c plots the Schottky barrier height and the ideality factor as a function of temperature. The Schottky barrier height  $\Phi_{b0}$  increases with the temperature while the ideality factor n decreases. This behavior confirms that the thermionic emission is the dominant carrier conduction process at high temperature, while at lower temperature, the increase of n indicates the presence of other transport phenomena, such as the generation-recombination of charges in the depletion layer and tunneling through the barrier [16,17].

We studied the photoresponse of the device by shining light from the top, on the entire device. Figure 2d compares the room-temperature I-V curves obtained in darkness and at different illumination intensities from a white LED lamp. The forward current remains unchanged, while the reverse

*Nanomaterials* **2017**, *7*, 158 5 of 8

current increases until it exceeds the forward current at the maximum illumination of 5 mW/cm<sup>2</sup>. This photocurrent corresponds to a maximum responsivity  $\mathcal{R} = \left(I_{\text{light}} - I_{\text{dark}}\right)/P_{\text{in}} = 2.5 \text{ A/W},$ where  $P_{\rm in}$  is the incident optical power, and  $I_{\rm light}$  and  $I_{\rm dark}$  are the reverse currents at  $V=-2.5~{

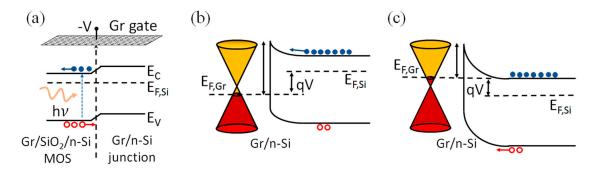

m V}$ with and without illumination, respectively. Figure 2e,f displays the reverse current at V=-2.4 Vin a sequence of light ON/OFF pulses, and show that the photoresponse of the device is limited by the measurement rate of our source measurement unit (2 Hz). The high photocurrent is the result of the peculiar geometry of the device, which is composed of the Gr/Si diode in parallel with the Gr/SiO<sub>2</sub>/Si MOS capacitor. In forward bias, the positive voltage on graphene causes accumulation of electrons (majority carriers) at the Si/SiO<sub>2</sub> interface of the MOS capacitor. These electrons do not affect the forward current of the Gr/Si diode, which is controlled by the injection rate of electrons over the barrier. In reverse bias, the electrons cannot overcome the barrier, and the saturation current is mainly due to minority carriers (holes). The reverse current can thus be increased by enhancing the concentration of minority carriers, e.g., by shining light. Upon illumination, photogenerated holes are attracted by the negative bias of graphene to the Si/SiO<sub>2</sub> interface of the MOS region. Their diffusion to Gr/Si junction originates the observed high photocurrent. Indeed, the motion of such holes to the Gr/Si junction is favored by the band bending from the Gr/SiO<sub>2</sub>/Si to the Gr/Si region, as shown by the band diagrams of Figure 3.

**Figure 3.** (a) Band diagram of the n-type Si substrate along the surface below the  $Gr/SiO_2/Si$  MOS capacitor and the Gr/Si diode, showing that diffusion of photogenerated holes towards the diode area is energetically favored. Band diagram of the Gr/Si junction in (b) forward and (c) reverse bias (the thin tunneling  $SiO_2$  interfacial layer is omitted).

It has been shown that the same mechanism, when applied to thermally generated minority carriers, contributes to the high leakage of the Gr/Si junctions [16].

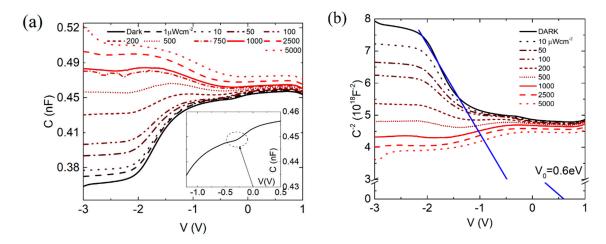

To further investigate the carrier distribution in the graphene-controlled Si substrate, we performed a room-temperature capacitance-voltage (C-V) characterization in the dark and under illumination (Figure 4). The capacitance measurements were performed in the -3 V to 1 V dc bias range and with ac small-signal of 100 mV amplitude and 10 kHz frequency.

Focusing on the dark curve (black solid line) in Figure 4a, it can be noticed that the measured capacitance is dominated by the MOS capacitor, which is in accumulation, at positive bias. As the voltage is lowered below zero, the MOS enters the weak depletion region, which corresponds to a decreasing capacitance. However, a change in the capacitance behavior occurs at  $V \approx -0.25$  V, as highlighted in the inset of the figure. The decreasing capacitance in the range -2 V < V < -0.25 V is likely dominated by the depletion capacitance of the reverse biased Schottky diode. For V < -2 V, the quasi bias-independent capacitance indicates that the MOS, which is now in deep inversion, dominates again over the Schottky diode. Below -2 V, the minority carriers are not able to follow the 10 kHz oscillations, and the MOS is in deep depletion, with the capacitance at its lowest plateau value (the reverse-bias decreasing capacitance of the Schottky diode is negligible in this region). Under high illumination, electron-hole pairs are photogenerated in the depletion region and holes accumulate at the Si/SiO<sub>2</sub> interface forming an inversion channel, which raises the MOS capacitance to a value

Nanomaterials **2017**, 7, 158 6 of 8

comparable to the one in accumulation at positive voltage. Otherwise stated, at the lowest biases and under high illumination, the device shows the typical C-V plots of a MOS on p-type semiconductor. This indicates that the photogeneration rate is able to provide enough positive charge to invert the n-Si and that the channel can follow the oscillation of the small ac signal.

**Figure 4.** (a) Small-signal (100 mV and 10 kHz) C-V measurements in dark and under different illumination levels. The inset highlights a crossover point between two regions where the capacitance of the device is dominated by the Schottky diode (V < -0.25 V) and the MOS capacitor (V > -0.25 V), respectively. (b)  $\frac{1}{C^2} - V$  plot of the device under study.

The holes of the inversion channel of the MOS capacitor, injected in the Gr/Si region, cause the high photocurrent of the device, as previously stated.

The interpretation of the Gr/Si dominating capacitance in the range -2 V < V < -0.25 V is confirmed by the linear behavior of the  $1/C^2$  vs. V plot, shown in Figure 4b. For a Schottky non-ideal diode the inverse square of reverse-bias capacitance is a linear function of the bias [16]:

$$\frac{1}{C^2} = \frac{2n[n(\Phi_{b0} - \Phi_n - kT) - qV]}{A^2q^2\varepsilon_{\rm S}N_{\rm d}},\tag{10}$$

where  $N_{\rm d}$  is the doping density,  $\varepsilon_{\rm S}=11.7\varepsilon_0$  is the silicon permittivity, and  $\Phi_{\rm n}=kT\ln N_{\rm c}/N_{\rm d}$  with  $N_{\rm c}=12\left(2\pi m^*~kTh^{-2}\right)^{\frac{3}{2}}$ , the effective density of states in the conduction band. According to Equation (10), the barrier height  $\Phi_{\rm b0}$  can be evaluated from the x-intercept,  $V_0$ , of the straight line fitting the  $1/C^2$  vs. V plot and results

$$\Phi_{b0} = \frac{V_0}{n} + kT \ln\left(\frac{N_c}{N_d}\right) + kT \approx 0.47 \text{eV},\tag{11}$$

$(N_{\rm d}=4.5\times 10^{14}~{\rm cm^{-3}}$  is the substrate doping and n=3.8 is the measured room-temperature ideality factor). The obtained value of  $\Phi_{\rm b0}$  is close to the barrier height extracted from the Richardson's plot and from the Cheung's method.

A similar model has been recently proposed in [18], where photocharge generation in the  $Gr/SiO_2/Si$  MOS region has been confirmed by scanning photocurrent measurements. High responsivity, broadband and fast Gr/Si photodetectors were also reported in [19,20].

## 3. Materials and Methods

The device was fabricated from a lightly doped n-silicon wafer with a resistivity of  $10~\Omega$ cm. A SiO<sub>2</sub> layer with a thickness of  $\sim 245$  nm was deposited by chemical vapor deposition (CVD), after that a  $10~\mu$ m-wide trench was patterned by lithography. The SiO<sub>2</sub> layer was removed from the trench area by

Nanomaterials **2017**, 7, 158

a hydrofluoric acid treatment immediately before graphene deposition. This procedure reduced the possibility that oxide will form on the surface. The graphene sheet had been obtained by CVD on Cu foil. In the next step, a graphene sheet of  $\sim 1\times 0.4~\text{cm}^2$  was deposited on the wafer, acting both as anode of the Gr/Si junction and top electrode of the Gr/SiO<sub>2</sub>/Si MOS capacitor. Ohmic metal contact to graphene was fabricated by evaporating a Ti/Au metal stack through a shadow mask, while the Si substrate was contacted by depositing Ag paste on an area with removed SiO<sub>2</sub> and appropriately scratched to produce ohmic contact. For I-V and C-V measurements, the Ti/Au pad was the forcing lead (anode) while the Ag contact on the Si substrate was grounded. Further information about the fabrication process can be found in [16]. Both the I-V and C-V characterizations were performed with the two-probe method, using a Keithley 4200-SCS and a Janis ST-500 micromanipulated probe station. The photoresponse was investigated using a light source consisting of an array of white LEDs with controllable intensity up to 5 mW/cm² and spectrum in the range 420 – 720 nm with two peaks at 454 nm and 536 nm, respectively.

#### 4. Conclusions

In conclusion, we characterized a hybrid device consisting of a Gr/Si junction in parallel with a  $Gr/SiO_2/Si$  MOS capacitor. We used I-V curves at different temperatures to extract the relevant parameters of the Schottky junction. More importantly, we reported a very high photocurrent, which can exceed the forward current. Using C-V characterization, we proved that the MOS capacitor acts as a reservoir of photo-generated minority carriers. Such excess minority carrier injected into the junction region is the origin of the observed high reverse photocurrent. Hence, the parasitic MOS capacitor enhances the photoresponse of the Gr/Si diode.

**Acknowledgments:** We thank Materials Research Department, IHP-Microelectronics, Frankfurt Oder, Germany, for the fabrication of the devices.

**Author Contributions:** A.D.B. conceived and designed the experiments; G.L., L.G., L.I. and N.M. performed the experiments; G.L., A.D.B. and F.G. analyzed the data; A.D.B. and N.M. contributed reagents/materials/analysis tools; G.L., A.D.B. and F.G. wrote the paper.

**Conflicts of Interest:** The authors declare no conflict of interest.

### References

- 1. Pop, E.; Varshney, V.; Roy, A.K. Thermal properties of graphene: Fundamentals and applications. *MRS Bull.* **2012**, *37*, 1273–1281. [CrossRef]

- 2. Castro Neto, A.H.; Guinea, F.; Peres, N.M.R.; Novoselov, K.S.; Geim, A.K. The electronic properties of graphene. *Rev. Mod. Phys.* **2009**, *81*, 109–162. [CrossRef]

- 3. Di Bartolomeo, A.; Santandrea, S.; Giubileo, F.; Romeo, F.; Petrosino, M.; Citro, R.; Barbara, P.; Lupina, G.; Schroeder, T.; Rubino, A. Effect of back-gate on contact resistance and on channel conductance in graphene-based field-effect transistors. *Diam. Relat. Mater.* **2013**, *38*, 19–23. [CrossRef]

- 4. Di Bartolomeo, A.; Giubileo, F.; Romeo, F.; Sabatino, P.; Carapella, G.; Iemmo, L.; Schroeder, T.; Lupina, G. Graphene field effect transistors with niobium contacts and asymmetric transfer characteristics. *Nanotechnology* **2015**, *26*, 475202. [CrossRef] [PubMed]

- 5. Giubileo, F.; di Bartolomeo, A. The role of contact resistance in graphene field-effect devices. *Prog. Surf. Sci.* **2017**, 92, 143–175. [CrossRef]

- 6. Xia, F.; Perebeinos, V.; Lin, Y.; Wu, Y.; Avouris, P. The origins and limits of metal? Graphene junction resistance. *Nat. Nanotechnol.* **2011**, *6*, 179–184. [CrossRef] [PubMed]

- 7. Di Bartolomeo, A.; Giubileo, F.; Iemmo, L.; Romeo, F.; Russo, S.; Unal, S.; Passacantando, M.; Grossi, V.; Cucolo, A.M. Leakage and field emission in side-gate graphene field effect transistors. *Appl. Phys. Lett.* **2016**, 109, 023510. [CrossRef]

- 8. Niu, G.; Capellini, G.; Hatami, F.; di Bartolomeo, A.; Niermann, T.; Hussein, E.H.; Schubert, M.A.; Krause, H.-M.; Zaumseil, P.; Skibitzki, O.; et al. Selective Epitaxy of InP on Si and Rectification in Graphene/InP/Si Hybrid Structure. ACS Appl. Mater. Interfaces 2016, 8, 26948–26955. [CrossRef] [PubMed]

*Nanomaterials* **2017**, *7*, 158 8 of 8

9. Bonaccorso, F.; Sun, Z.; Hasan, T.; Ferrari, A.C. Graphene photonics and optoelectronics. *Nat. Photonics* **2010**, 4, 611–622. [CrossRef]

- 10. Di Bartolomeo, A. Graphene Schottky diodes: An experimental review of the rectifying graphene/semiconductor heterojunction. *Phys. Rep.* **2016**, *606*, 1–58. [CrossRef]

- 11. Liang, S.J.; Hu, W.; di Bartolomeo, A.; Adam, S.; Ang, L.K. A modified Schottky model for graphene-semiconductor (3D/2D) contact: A combined theoretical and experimental study. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016. [CrossRef]

- 12. Varonides, A. Combined thermionic and field emission reverse current for ideal graphene/n-Si Schottky contacts in a modified Landauer formalism. *Phys. Status Solidi C* **2016**, *13*, 1040–1044. [CrossRef]

- 13. Sze, S.M.; Ng, K.K. *Physics of Semiconductor Devices*, 3rd ed.; Wiley-Interscience: Hoboken, NJ, USA, 2007; ISBN 978-0-471-14323-9.

- 14. Card, H.C.; Rhoderick, E.H. Studies of tunnel MOS diodes I. Interface effects in silicon Schottky diodes. *J. Phys. D Appl. Phys.* **1971**, *4*, 1589–1601. [CrossRef]

- 15. Cheung, S.K.; Cheung, N.W. Extraction of Schottky diode parameters from forward current-voltage characteristics. *Appl. Phys. Lett.* **1986**, *49*, 85–87. [CrossRef]

- 16. Di Bartolomeo, A.; Luongo, G.; Giubileo, F.; Funicello, N.; Niu, G.; Schroeder, T.; Lisker, M.; Lupina, G. Hybrid graphene/silicon Schottky photodiode with intrinsic gating effect. 2D Mater. 2017, 4, 025075. [CrossRef]

- 17. Di Bartolomeo, A.; Giubileo, F.; Luongo, G.; Iemmo, L.; Martucciello, N.; Niu, G.; Fraschke, M.; Skibitzki, O.; Schroeder, T.; Lupina, G. Tunable Schottky barrier and high responsivity in graphene/Si-nanotip optoelectronic device. 2D Mater. 2017, 4, 015024. [CrossRef]

- 18. Riazimehr, S.; Kataria, S.; Bornemann, R.; Haring Bolívar, P.; Ruiz, F.J.G.; Engström, O.; Godoy, A.; Lemme, M.C. High Photocurrent in Gated Graphene–Silicon Hybrid Photodiodes. *ACS Photonics* **2017**, 4, 1506–1514. [CrossRef]

- 19. Chen, Z.; Cheng, Z.; Wang, J.; Wan, X.; Shu, C.; Tsang, H.K.; Ho, H.P.; Xu, J.B. High Responsivity, Broadband, and Fast Graphene/Silicon Photodetector in Photoconductor Mode. *Adv. Opt. Mater.* **2015**, *3*, 1207–1214. [CrossRef]

- 20. Wang, J.; Cheng, Z.; Chen, Z.; Wan, X.; Zhu, B.; Tsang, H.K.; Shu, C.; Xu, J. High-responsivity graphene-on-silicon slot waveguide photodetectors. *Nanoscale* **2016**, *8*, 13206–13211. [CrossRef] [PubMed]

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).