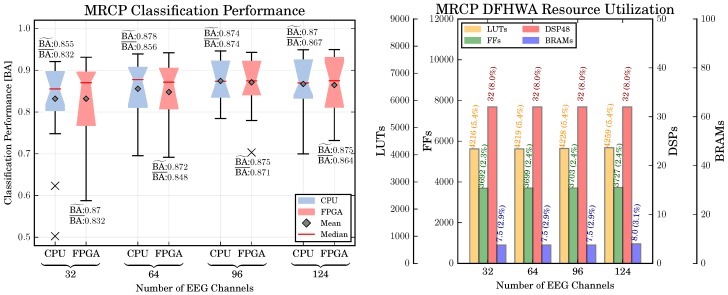

Figure 8.

Left: Classification performance for the detection of the MRCP for CPU and FPGA for 32–124 channels. The median () and mean () classification performance is reported for each case. Right: Resource utilization of the DFHWA for different numbers of EEG channels. The percentage values refer to the amount of resources provided by the Zynq ZC7030.