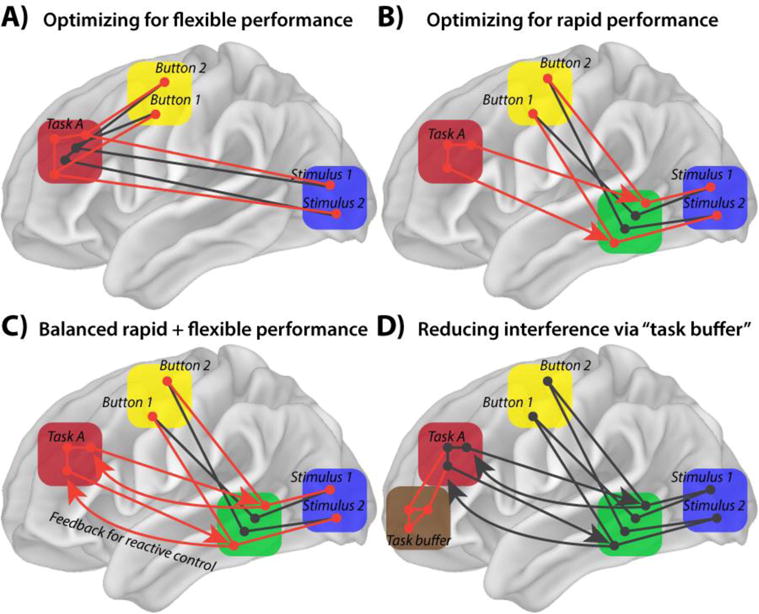

Figure 4. Alternative brain network mechanisms for RITL and reflexivity.

Lateral PFC (red box) represents example Task A, with red circles and lines indicating activated neural populations and functional connections, respectively. A simple task set is depicted, with Stimulus 1 (e.g., the letter “T”) leading to Button 2 (e.g., pressing with the right index finger), and Stimulus 2 (e.g., the letter “S”) leading to Button 1 (e.g., pressing with the left index finger). The yellow box represents primary motor cortex, the blue box visual cortex, the green box posterior association cortex, and the brown box anterior PFC. A) A theoretical network architecture consistent with optimized flexible performance is depicted. However, this scenario would slow down processing due to requiring all task-related activity to flow through PFC, which is a long distance from the sensory input (requiring additional action potential propagation time). B) An alternative scenario involves preparatory top-down signals from lateral PFC to posterior association cortex (green box) closer to both motor and sensory regions. This would engender a faster flow of activity from the visual to motor regions. However, this would produce interference if a target stimulus was presented during a secondary or intermediate task (as in the NEXT paradigm), resulting in an increase of errors. C) We postulate the existence of an architecture in which multimodal associative activity is monitored for errors by lateral PFC (or anterior cingulate cortex). This would allow for online, reactive control of performance at the cost of slowing down performance. However, some slowing may be useful for preventing errors, based on a more complete representation of the full task context within lateral PFC (relative to posterior multimodal cortex). D) A potentially more effective way to reduce interference during, e.g., NEXT task performance is to temporarily store the Task A representation in a “task buffer”. This buffer is removed from immediate embodied representations, allowing for task representation maintenance without interference with ongoing task performance.