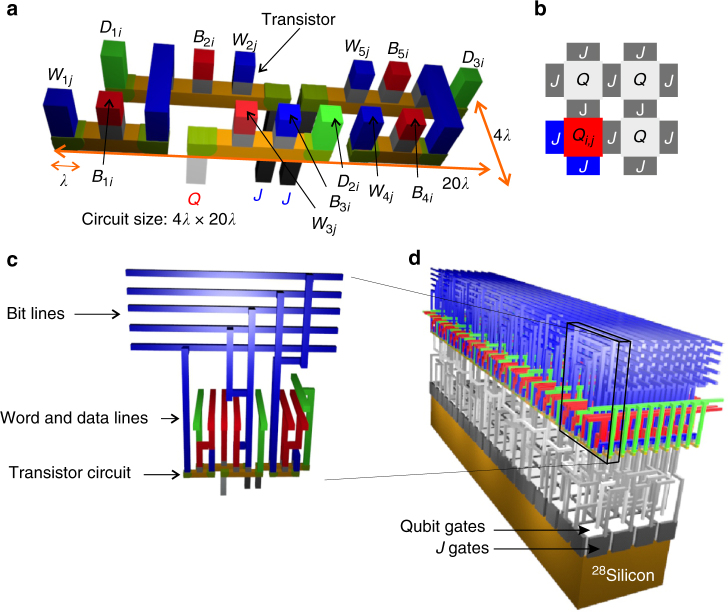

Fig. 2.

Quantum processor integration scheme. a Physical circuit for a single qubit and two J-gates (see schematic b). The gray elements in a correspond to the transistor switches used to activate a line. The scale λ is the features size, which is presumed constant for each metal or dielectric layer. c Same as a, but from a different perspective, in order to show how word, bit, and data lines connect with the unit cell. d In order to match the difference in aspect ratios between the qubit layer and control layer, the control elements for a single qubit and two J-gates are extended to a 4 × 20 qubit array. Another extension must be made to accommodate for the surface code sequences shown in Fig. 4, so that a single qubit module becomes a 24 × 20 qubit array, as depicted in Fig. 1