Received: 11 October 2017 Accepted: 5 February 2018

Published online: 16 February 2018

# **OPEN** A soft lithographic approach to fabricate InAs nanowire field-effect transistors

Sang Hwa Lee 1, Sung-Ho Shin2, Morten Madsen 3, Kuniharu Takei4, Junghyo Nah 2 & Min Hyung Lee 101

The epitaxial layer transfer process was previously introduced to integrate high-quality and ultrathin III-V compound semiconductor layers on any substrate. However, this technique has limitation for fabrication of sub-micron nanoribbons due to the diffraction limit of photolithography. In order to overcome this limitation and scale down its width to sub-50 nm, we need either a costly short wavelength lithography system or a non-optical patterning method. In this work, high-quality III-V compound semiconductor nanowires were fabricated and integrated onto a Si/SiO2 substrate by a softlithography top-down approach and an epitaxial layer transfer process, using MBE-grown ultrathin InAs as a source wafer. The width of the InAs nanowires was controlled using solvent-assisted nanoscale embossing (SANE), descumming, and etching processes. By optimizing these processes, NWs with a width less than 50 nm were readily obtained. The InAs NWFETs prepared by our method demonstrate peak electron mobility of ~1600 cm<sup>2</sup>/Vs, indicating negligible material degradation during the SANE process.

The scaling of Si-based metal-oxide-semiconductor field-effect transistors (MOSFETs) has played an important role in achieving high performance devices with low power consumption and has produced tremendous economic benefits<sup>1,2</sup>. This trend has continued to date, following Moore's law<sup>3</sup>. As the scaling of Si-based devices approaches its fundamental limit, however, alternative channel materials, such as III-V compound semiconductors<sup>4-6</sup>, carbon-based nanomaterials<sup>7-9</sup>, and layered semiconductors<sup>10-12</sup>, have gained attention. Among these materials, III-V compound semiconductors have been considered as next-generation channel materials due to their exceptionally high electron mobility.

Although the performance of III-V MOSFETs exceeds that of Si MOSFETs, high material costs and difficult integration of III-V materials onto conventional Si substrates have hindered the growth of III-V MOSFET industries. Recently, the epitaxial lift-off and transferring (ELT) technique was developed to integrate ultrathin III-V semiconductor layers onto Si/SiO<sub>2</sub> substrate<sup>13</sup>. This method allows facile integration of different III-V materials with huge lattice mismatches on the same substrate, which has been one of the main obstacles for their use in future device applications. Using this technique, high performance III-V MOSFETs, complementary metal-oxide-semiconductor (CMOS) logic circuits<sup>14</sup>, and radio frequency (RF) circuits<sup>15</sup> on both Si/SiO<sub>2</sub> substrates and flexible substrates have been demonstrated. However, this technique has limitation for fabrication of sub-micron nanoribbon-based FETs due to the diffraction limit of photolithography. In order to overcome this limitation and scale down its width to sub-50 nm nanowires (NWs), we need either a costly short wavelength lithography system<sup>16</sup> or a non-optical patterning method<sup>17</sup>.

Here, we present a modified ELT technique to fabricate sub-50 nm width InAs NWs. Specifically, the InAs NW was fabricated using soft lithography, called solvent-assisted nanoscale embossing (SANE), using epitaxially grown InAs thin film on the buffer layers. Using the transferred NWs on a SiO<sub>2</sub>/Si substrate, InAs NWFETs were fabricated and exhibited high on/off current ratio (~104) and peak electron mobility (~1600 cm2V-1s-1), indicating that our approach is a reliable way to form one-dimensional nanomaterials from 2-D thin films.

<sup>1</sup>Department of Applied Chemistry, Kyung Hee University, Yongin, Gyeonggi, 17104, Korea. <sup>2</sup>Department of Electrical Engineering, Chungnam National University, Daejeon, 34134, Korea. <sup>3</sup>SDU NanoSYD, Mads Clausen Institute University of Southern Denmark, Alsion 2, 6400, Sønderborg, Denmark. Department of Physics and Electronics, Osaka Prefecture University, Sakai, Osaka, 599-8531, Japan. Sang Hwa Lee and Sung-Ho Shin contributed equally to this work. Correspondence and requests for materials should be addressed to J.N. (email: jnah@cnu.ac.kr) or M.H.L. (email: minhlee@khu.ac.kr)

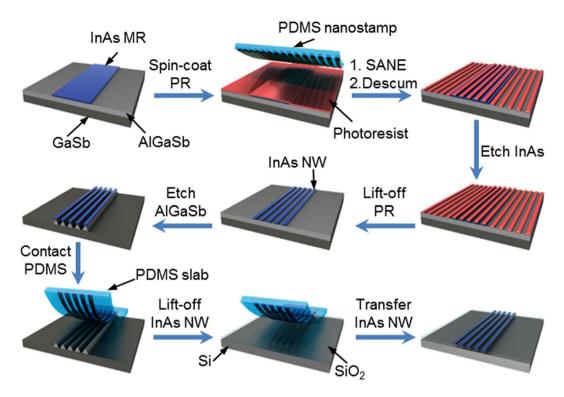

**Figure 1.** Schematic representation of sub-50 nm InAs NWs transferred to Si/SiO<sub>2</sub>.

#### Results

Fabrication of sub-50 nm InAs NWs using SANE and ELT. Figure 1 shows a schematic representation of fabrication of sub-50 nm NWs using a simple soft lithographic approach. A molecular beam epitaxy (MBE)grown InAs/Al<sub>0.7</sub>Ga<sub>0.8</sub>Sb/GaSb wafer was used to fabricate the NW. A 5-µm-wide InAs microribbon (MR) was fabricated using conventional photolithography, followed by wet etching of InAs in a mixture of citric acid and H<sub>2</sub>O<sub>2</sub>. The SANE process was then carried out on MRs to create sub-50 nm photoresist (PR) lines on the NRs. A polydimethylsiloxane (PDMS) stamp (with lines 70 nm wide and 140 nm apart), soaked with a drop of dimethyl formamide (DMF), was applied to InAs MRs coated with the photoresist (Shipely S1805). After the DMF was dried, the stamp was detached, leaving uniform PR lines (~50 nm wide and 140 nm apart). Even though residual layers between PR lines were not observable, 5~10 sec of O<sub>2</sub> plasma descumming was performed to remove potential PR residues. During the descumming process, the width of PR lines was further decreased by increasing the duration of descumming, as described later. Using nano-PR lines as an etching mask, the InAs layer was then etched with a citric acid/H<sub>2</sub>O<sub>2</sub> mixture, followed by removal of the PR lines. A sacrificial AlGaSb layer was selectively etched using NH<sub>4</sub>OH, forming InAs NWs on an AlGaSb pedestal. A slab of PDMS was then gently pressed against the patterned wafer, which transfers partially released InAs NWs onto the PDMS. The InAs NWs on PDMS were then treated with dilute HF solution (1:50) for 1 min to remove residual AlGaSb. Finally, the PDMS slab with InAs NWs was pressed onto a clean Si/SiO<sub>2</sub> wafer to transfer the InAs NWs.

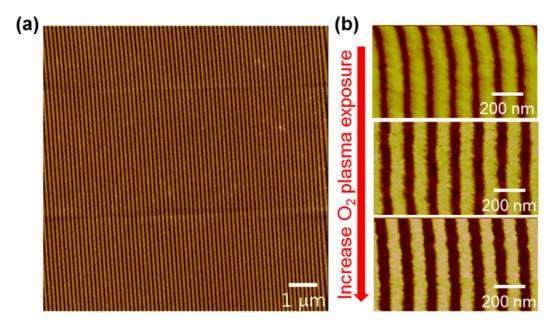

Characterization of sub-50 nm InAs NWs. Figure 2a shows the atomic force micrograph (AFM) of uniform PR-line patterns formed over a large area by the SANE process. The SANE process is a critical step in determining the width and electrical properties of InAs NWs for two reasons. First, it can generate sub-100 nm wide PR lines, overcoming the diffraction limit of photolithography. Second, nano-PR lines created by the SANE process are smoother than those created by photolithography. Therefore, the subsequent etching process produces semiconductor NWs with smooth edges, which result in high channel mobility due to reduced scattering from the NW surface<sup>18</sup>. Here, the NW width was reduced by adjusting oxygen plasma processing time on patterned PR lines, where the PR line width was gradually decreased with process time increase (Fig. 2b). However, a long descumming process can cause rough edges on PR lines and reduce the height of PR patterns, necessitating optimization of the process time. After scaling the PR lines, the width of the InAs NWs was further decreased by subsequent InAs wet-etching. We note that the width of PR line patterns can be scaled down further by selecting a solvent with a high swelling factor of the PDMS molds (swelling factor  $S = D/D_0$ , where D is the length of PDMS in the solvent, and  $D_0$  is the length of the PDMS in air). As we described in this report, the SANE process using DMF ( $S \sim 1.02$ ) can decrease PR lines by 22% ( $\sim 50$ -nm PR line patterns) using the PDMS mold with 70-nm lines. For further width scaling, solvent with a higher S such as isopropyl alcohol ( $S \sim 1.09$ ) or dichloromethane ( $S \sim 1.09$ ) or 1.22) can be used, which can reduce the PR lines by 33% (~45 nm PR lines) and 44% (~40 nm PR lines), respectively<sup>19</sup>. Our method is capable of achieving high scaling down factors with all soft lithography methods (SANE and ELT) and producing features down to 30 nm in size without using expensive DUV or e-beam lithography.

**Figure 2.** Atomic force micrographs of photoresist line patterns after the SANE process. (a) SANE-patterned photoresist over a large area. (b) Reduced photoresist line width with increasing  $O_2$  plasma etching time.

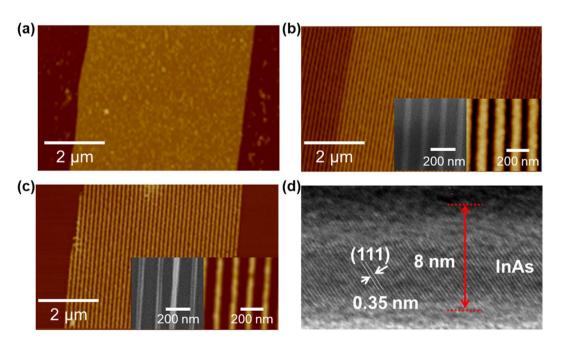

**Figure 3.** Atomic force micrographs of **(a)** InAs microribbon, **(b)** SANE photoresist pattern on InAs microribbon (inset: SEM and AFM images of 50-nm PR lines), **(c)** InAs NWs (inset: SEM and AFM images of 35-nm InAs NWs), **(d)** Transmission electron micrograph of the InAs NWs transferred onto Si/SiO<sub>2</sub>.

Figure 3 shows AFM images of InAs NWs obtained by SANE and ELT process. The 5- $\mu$ m InAs MRs were first patterned using conventional photolithography, followed by etching InAs film using micro-PR lines as an etch mask (Fig. 3a). We performed this step to fabricate hierarchical patterns of NWs. After performing SANE on the MR patterned wafers using DMF-soaked PDMS with line patterns (70 nm wide and 140 nm pitch), 50-nm-wide PR lines were created over InAs MRs, exposing the AlGaSb layer (Fig. 3b). The PR lines were decreased by approximately 20% due to swelling of PDMS in DMF<sup>20</sup>. The InAs MRs were then etched again using 50-nm PR lines as an etch mask, producing sub-50 nm InAs NW bundles in each 5- $\mu$ m section of InAs MR. Afterward, the remaining PR was cleaned with acetone. The InAs NWs transferred onto a fresh Si/SiO<sub>2</sub> (50 nm) substrate had a width of ~35 nm (Fig. 3c inset) because of undercutting during wet chemical etching. The NW width can be further decreased by increasing InAs etching time. The NW edges and surface were smooth due to fine PR pattern formation after SANE and etching of residual InAs in dilute HF (Fig. 3c). Figure 3d shows a cross-sectional

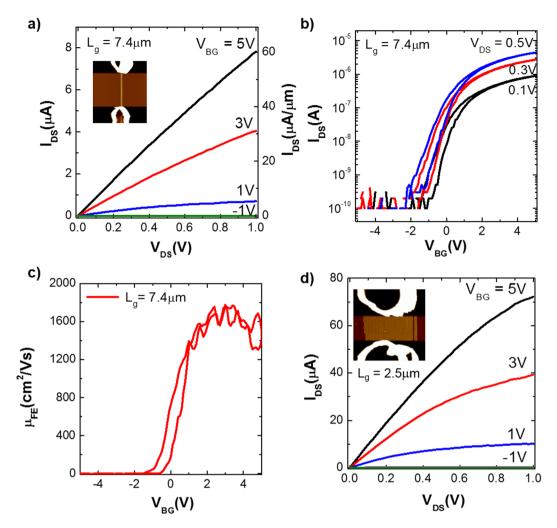

Figure 4. Electrical characteristics of the back-gated InAs NWFETs. (a) Output ( $I_{DS}$ - $V_{DS}$ ) and (b) transfer ( $I_{DS}$ - $V_{BG}$ ) characteristics of the InAs NWFET with a channel length of ~7.4  $\mu m$  and a total NW width of ~130 nm. The right axis in (a) shows  $I_{DS}$  normalized by the total NW width. (c) Field-effect mobility vs.  $V_{BG}$ , calculated at  $V_{DS}$ =0.1 V for the same device. (d) The  $I_{DS}$ - $V_{DS}$  data of the InAs NWFET with a channel length of high density NW bundles of ~2.5  $\mu m$ , comprising ~25 NWs.

transmission electron micrograph (TEM) of an InAs NW transferred to a Si/SiO $_2$  substrate, demonstrating a single crystalline structure. The active InAs layer was ~8 nm thick, and the native oxide was ~2 nm thick.

**Electrical characteristics of the InAs NWFETs.** To evaluate the electrical characteristics of the InAs NWs, we fabricated back-gated NWFETs. The electrical characteristics of the InAs NWFET with three NWs, having a 130 nm total channel width and a 7.4 μm channel length, are shown in Fig. 4a–c. The drain current (I<sub>DS</sub>) increased linearly with V<sub>DS</sub> until it saturated, suggesting that PR residue from the SANE process does not remain on InAs NWs (Fig. 4a). The InAs NWFET exhibited a high ON-state current of ~33 μA/μm and an OFF-state current below 2 nA/μm at V<sub>DS</sub>=0.5 V, resulting in a high ON/OFF current ratio, ~10<sup>4</sup> (Fig. 4b). The field-effect mobility was calculated as a function of V<sub>BG</sub> using the standard square law model for electron mobility  $\mu_{n,FE} = g_m (L_g^2/C_{ox}V_{DS})$ , where  $g_m$  is the transconductance,  $g_m = dI_{DS}/dV_{BG}|_{V_{DS}=0.1V}$  and  $C_{ox}$  is the gate-to-NW capacitance, (Fig. 4c). The calculated peak electron mobility was ~1600 cm²/Vs, which excels or is comparable to that of InAs NR FET with the same layer thickness, indicating negligible mobility degradation due to width scaling <sup>13</sup>.

By increasing the number of NWs composing the channel, a NWFET with a channel length of 2.5  $\mu$ m was fabricated (Fig. 4d) with ~25 InAs NW bundles. The NWFET exhibited approximately 10-fold higher ON-state current by comparison to the data in Fig. 4a, demonstrating that current level modulation can be achieved by adjusting the number of NWs. The number of NWs transferred onto the Si/SiO<sub>2</sub> substrate can be varied by adjusting the adhesion between the InAs NWs and PDMS stamp. Using h-PDMS (hard PDMS) with low adhesion, 3~5 NWs were transferred to the Si/SiO<sub>2</sub> wafers. With high adhesion PDMS (soft PDMS), high-density NWs can be transferred at a high yield.

#### Discussion

In this paper, we report a simple soft nanolithographic approach to obtain NWs from an epitaxially grown III-V wafer. Using this technique, high-quality NWs were reliably produced from a 2 D semiconductor layer, which can be potentially used to realize III-V NWFETs on any substrate. To gauge the quality of NWs, the InAs NWFETs were fabricated and investigated. The enhanced device performance, observed in these NWFETs by comparison to InAs NRFETs<sup>13</sup>, indicates the reliability of our approach. In addition, the device current modulation was demonstrated by controlling the density of transferred NWs. Our approach can also provide a way to create a one-dimensional device structure out of 2 D source materials to study low dimensional physics and can be employed for various device applications.

#### Methods

**PDMS** nanostamp preparation. hard-PDMS/soft-PDMS nanostamps were prepared by spin-coating hard-PDMS solution onto anti-sticking layer coated Si gratings (70-nm lines, 140-nm pitch, Lightsmyth, USA), followed by coating with soft-PDMS solutions (10:1 ratio mixture of prepolymer and curing agent, Sylgard 184, Dow Corning Co., USA) and curing at 70 °C for 2 hrs.

**InAs microribbon (MR) fabrication.** Conventional photolithography was performed on the surface of an i-line PR-coated MBE-grown InAs/Al $_{0.2}$ Ga $_{0.8}$ Sb/GaSb wafer, using a photomask with microline (5  $\mu$ m wide and 10  $\mu$ m pitch) patterns. Using the PR patterns as an etch mask, a 10-nm-thick InAs layer was etched with a mixture of citric acid (1 g per 1 ml of H $_2$ O) and 30% H $_2$ O $_2$  at 1:20 (v:v), and the PR was removed using ultrasonication with acetone.

**Solvent-assisted nanoscale embossing (SANE).** Photoresist (S1805, Rohm and Hass) was spincoated onto a handling wafer with InAs MRs. The surface of the pre-patterned PDMS nanostamp (lines of 70 nm wide and 140 nm pitch) was soaked with dimethylformamide (DMF) (Sigma-Aldrich) in a crystallizing dish, and it was immediately placed on the S1805-coated InAs MR source wafer. The sample was kept at room temperature without agitation until the DMF was completely dried. Then, the stamp was gently separated from the wafer.

**InAs nanowire (NW) fabrication.** The SANE patterned PR lines were treated with oxygen plasma (50 W, 50 sccm) for  $5 \sim 10$  s to remove residual PR between the nanolines. Using the PR patterns as an etch mask, the InAs MRs were etched using a mixture of citric acid and  $H_2O_2$ , forming InAs NWs.

**Transfer InAs NWs on Si/SiO2 wafer.** To release InAs NWs anchored on the source wafer, the AlGaSb sacrificial layer was anisotropically etched by  $NH_4OH$  (3% in water) solution for 10 min. Next, the 2-mm-thick soft-PDMS slab was gently pressed on the InAs NWs floated on AlGaSb pedestals and was smoothly detached from the source wafer. The InAs NWs on the PDMS slabs were then cleaned in a diluted HF (50:1) solution for 1 min to remove any residues of sacrificial layer on the InAs NWs. The InAs NWs were transferred by gently pressing the PDMS slab onto a Si/SiO<sub>2</sub> (50-nm thick thermally grown SiO<sub>2</sub>) wafer.

**NWFET fabrication.** The back-gated NWFETs were fabricated by depositing Ni (50 nm) on photolithographically defined source/drain regions of the transferred InAs NWs.

#### References

- Dennard, R. H., Gaensslen, F. H., Rideout, V. L., Bassous, E. & LeBlanc, A. R. Design of Ion-Implanted Mosfet's with Very Small Physical Dimensions. *IEEE J. Solid-State Circuit* 9, 256–268 (1974).

- 2. Ferain, I., Colinge, C. A. & Colinge, J.-P. Multigate Transistors as the Future of Classical Metal-Oxide-Semiconductor Field-Effect Transistors. *Nature* 479, 310–316 (2011).

- 3. Chau, R., Doyle, B., Datta, S., Kavalieros, J. & Zhang, K. Integrated Nanoelectronics for the Future. Nat. Mater. 6, 810-812 (2007).

- 4. del Alamo, J. A. Nanometre-Scale Electronics with Iii-V Compound Semiconductors. Nature 479, 317-323 (2011).

- 5. Takahashi, T. *et al.* Parallel Array Inas Nanowire Transistors for Mechanically Bendable, Ultrahigh Frequency Electronics. *ACS Nano* 4, 5855–5860 (2010).

- 6. Chuang, S. et al. Ballistic Inas Nanowire Transistors. Nano Lett. 13, 555-558 (2012).

- 7. Franklin, A. D. & Chen, Z. Length Scaling of Carbon Nanotube Transistors. Nat. Nanotechnol. 5, 858-862 (2010).

- 8. Lin, Y.-M. et al. Wafer-Scale Graphene Integrated Circuit. Science 332, 1294–1297 (2011).

- 9. Wang, C., Takei, K., Takahashi, T. & Javey, A. Carbon Nanotube Electronics Moving Forward. Chem. Soc. Rev. 42, 2592–2609 (2013).

- 10. Radisavljevic, B., Radenovic, A., Brivio, J., Giacometti, V. & Kis, A. Single-Layer Mos<sub>2</sub> Transistors. Nat. Nanotechnol. 6, 147-150 (2011).

- 11. Fang, H. et al. High-Performance Single Layered Wse2 P-Fets with Chemically Doped Contacts. Nano Lett. 12, 3788–3792 (2012).

- 12. Kim, S. et al. High-Mobility and Low-Power Thin-Film Transistors Based on Multilayer Mos2 Crystals. Nat. Commun. 3, 1011 (2012)

- Ko, H. et al. Ultrathin Compound Semiconductor on Insulator Layers for High-Performance Nanoscale Transistors. Nature 468, 286–289 (2010).

- 14. Nah, J. et al. Iii–V Complementary Metal–Oxide–Semiconductor Electronics on Silicon Substrates. Nano Lett. 12, 3592–3595 (2012).

- 15. Wang, C. et al. Self-Aligned, Extremely High Frequency Iii–V Metal-Oxide-Semiconductor Field-Effect Transistors on Rigid and Flexible Substrates. Nano Lett. 12, 4140–4145 (2012).

- 16. Hahmann, P., Boettcher, M., Klein, M. W., Stolberg, I. A. & Weidenmueller, U. High Resolution Patterning Preparation of Vsb Systems for 22 nm Node Capability. *Microelectronic Engineering* 87, 1077–1081 (2010).

- 17. Cheong, L. L. et al. Thermal Probe Maskless Lithography for 27.5 Nm Half-Pitch Si Technology. Nano Letters 13, 4485–4491 (2013).

- 18. Lim, J., Hippalgaonkar, K., Andrews, S. C., Majumdar, A. & Yang, P. Quantifying Surface Roughness Effects on Phonon Transport in Silicon Nanowires. *Nano Lett.* 12, 2475–2482 (2012).

- 19. Lee, M. H., Huntington, M. D., Zhou, W., Yang, J.-C. & Odom, T. W. Programmable Soft Lithography: Solvent-Assisted Nanoscale Embossing. *Nano Lett.* 11, 311–315 (2010).

- Lee, J. N., Park, C. & Whitesides, G. M. Solvent Compatibility of Poly(Dimethylsiloxane)-Based Microfluidic Devices. Anal. Chem. 75, 6544–6554 (2003).

## **Acknowledgements**

This research was supported by the Creative Materials Discovery Program (NRF-2017M3D1A1039379) and Basic Science Research Program (NRF-2017R1A4A1015744) through the National Research Foundation of Korea (NRF) funded by the Ministry of Science and ICT.

#### **Author Contributions**

J.N. and M.H.L. designed the experiments. S.H.L., S.-H.S., M.M., K.T., J.N., and M.H.L. carried out experiments. S.H.L., S.-H.S., M.M., K.T., J.N., and M.H.L. contributed to the data analysis. S.H.L., S.-H.S., J.N., and M.H.L. wrote the paper.

## **Additional Information**

Competing Interests: The authors declare no competing interests.

**Publisher's note:** Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Open Access This article is licensed under a Creative Commons Attribution 4.0 International License, which permits use, sharing, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, provide a link to the Creative Commons license, and indicate if changes were made. The images or other third party material in this article are included in the article's Creative Commons license, unless indicated otherwise in a credit line to the material. If material is not included in the article's Creative Commons license and your intended use is not permitted by statutory regulation or exceeds the permitted use, you will need to obtain permission directly from the copyright holder. To view a copy of this license, visit http://creativecommons.org/licenses/by/4.0/.

© The Author(s) 2018