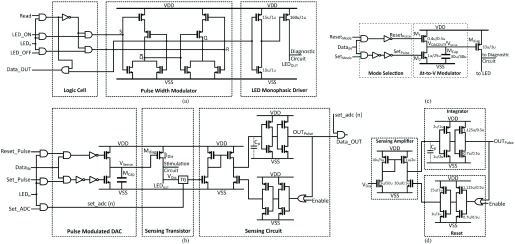

Fig. 6.

(a) Circuit schematic of stimulation control block.  signals determine the operation status of emitters. Read signal monitors the real-time working state saved by PWM unit. (b) A circuit schematic of diagnostic sensing block. Set_Pulse and Reset_Pulse generate pulse signals to achieve voltage scanning. Set_ADC determines the timing control of the

signals determine the operation status of emitters. Read signal monitors the real-time working state saved by PWM unit. (b) A circuit schematic of diagnostic sensing block. Set_Pulse and Reset_Pulse generate pulse signals to achieve voltage scanning. Set_ADC determines the timing control of the  ADC to fetch the

ADC to fetch the  . (TG is short for transmission gate). (c) Circuit schematic of the pulse width modulated DAC. This DAC performs two operations: mode selection and time-to-voltage conversion. (d) The diagnostic sensing element. Left is a (non-OTA) transconductance amplifier which feeds current into a simple

. (TG is short for transmission gate). (c) Circuit schematic of the pulse width modulated DAC. This DAC performs two operations: mode selection and time-to-voltage conversion. (d) The diagnostic sensing element. Left is a (non-OTA) transconductance amplifier which feeds current into a simple  ADC (right). This consists of three stages: current buffering, integration, and reset/pulse control.

ADC (right). This consists of three stages: current buffering, integration, and reset/pulse control.