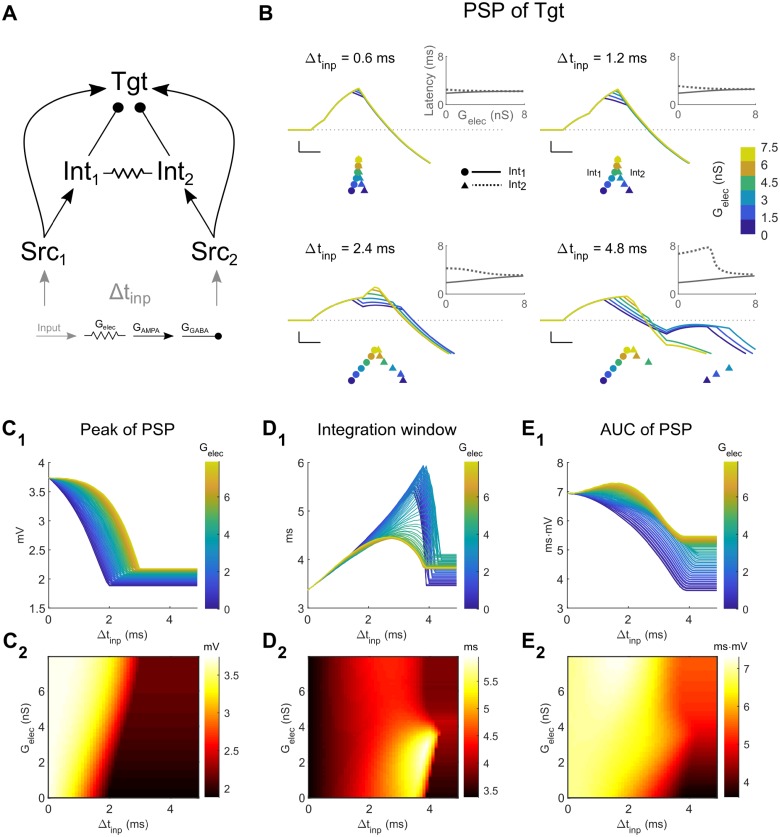

Fig 3. Coupled canonical circuit (CCC) model: Two Src neurons and two Int neurons lead to a common Tgt neuron.

A: Model schematic. For the simulations shown here, the Int neurons were electrically coupled. Each Src neuron receives its own input, with timing difference between the two inputs as Δtinp. B: Examples of Tgt PSPs for different electrical synapse strengths between interneurons in the network (colored lines and legends). Each subpanel represents different values of input timing differences Δtinp. Scale bar is 1 mV, 1 ms. Colored symbols below PSPs represent the spike times of Int1 (circle ●) and Int2 (triangle ▲). Symbols are vertically separated for clarity. Insets show latencies of Int1 (solid lines) and Int2 (dashed lines) spikes relative to Src1, against Gelec. C-E: Increased electrical coupling leads to increased peak and AUC of the Tgt PSP, and decreased the integration window.