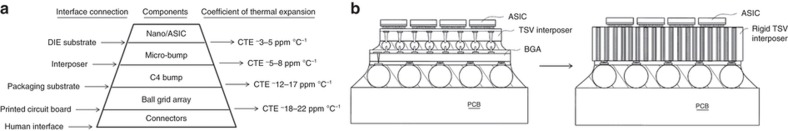

Figure 1.

(a) Interface pyramid showing the components in a conventional package, along with the estimated CTEs of the involved substrates. (b) Introducing a rigid 3D TSV interposer (right) to bridge the mismatch of the CTE values of the PCB board and the Si application-specific integrated circuit (ASIC) dies3. CTE, coefficients of thermal expansion; PCB, printed circuit boards; 3D TSV, three dimensional through silicon via.