Abstract

The through-silicon-vias (TSVs) process is a vital technology in microelectromechanical systems (MEMS) packaging. The current via filling technique based on copper electroplating has many shortcomings, such as involving multi-step processes, requiring sophisticated equipment, low through-put and probably damaging the MEMS devices susceptible to mechanical polishing. Herein, a room temperature treatable, high-efficient and low-cost seedless TSV process was developed with a one-step filling process by using novel electrically conductive adhesives (ECAs) filled with silver nanowires. The as-prepared ECAs could be fully cured at room temperature and exhibited excellent conductivity due to combining the benefits of both polymethyl methacrylate (PMMA) and silver nanowires. Complete filling of TSVs with the as-prepared 30 wt% silver nanowires ECAs was realized, and the resistivity of a fully filled TSV was as low as 10−3 Ω·cm. Furthermore, the application of such novel TSV filling process could also be extended to a wide range of different substrates, showing great potential in MEMS packaging, flexible microsystems and many other applications.

Keywords: seedless TSVs process, room temperature curing, electrically conductive adhesives, MEMS packaging, flexible microsystems

1. Introduction

As MEMS packaging evolves into miniaturization, TSV (through-silicon-vias) becomes a critical interconnection technology for MEMS packaging [1,2,3,4,5,6,7,8,9]. The current via-filling technique based on copper electroplating normally involves multi-step processes, including physical vapor deposition (PVD) or chemical vapor deposition (CVD) of barriers and copper seed layers, electroplating of copper plugs and the chemical mechanical polishing (CMP) process to remove the overburden layer and flatten the surface. This via-filling technique has been widely applied in TSV fabrication process benefiting from its low resistivity, capability of void-free fill, high reliability, and compatibility with the thermal budget [10,11,12,13,14,15,16,17,18,19]. However, the technique suffers from many limitations of either relying on sophisticated equipment (PVD, CVD, CMP, etc.), an unrealistic amount of pinch-off time, and sensitivity to process conditions under complex process parameters, as well as providing the risk of damage to the sensitive MEMS device if the via is fabricated after the device is finished. All these defects mentioned above make copper electroplating an unsuitable tool for TSV fabrication. Thus, it is essential and vital to explore a seedless, high-efficient and low-cost TSV fabrication method for MEMS packaging.

In recent years, great efforts have been made to improve the TSV fabrication process. The focus is mainly on the research of new filling methods and materials, including seedless electroplating [20,21], liquid-metal injection (SnZn, SnAu) [22,23], metal paste printing (Ag, Au, Cu) [24,25,26,27,28], etc. Among these improved methods, interest in liquid-metal injection and paste printing is currently growing apace and great progress has been made. For instance, Jiebin Gu et al. developed an efficient TSV technology based on liquid-metal injection with a customized nozzle wafer for MEMS packaging [23]. Lee Mi Do and co-workers reported a cost-effective via metallization method using a nano-Ag particle solution through four cycles of printing and heat evaporation [24]. Nevertheless, the aforementioned TSV fabrication methods are limited by complex processing steps, drastically reducing the efficiency of fabrication and universality of the approaches. Moreover, the heat curing process or high temperature treatment is also indispensable, which inevitably brings negative effects on performance of the devices susceptible to high temperature and limits their application in flexible microsystems. However, the question of how to realize vias in a flexible substrate is still a critical research topic, owing to the growing demand in internet of things (IOT) technologies for various applications [26,29,30,31], such as smart grid, food safety monitor, body sensor network, etc.

Silver nanowires, as one of the most important conductive materials, have attracted extensive attention for many applications, one of which is as a conductive filler in ECAs [32,33,34,35,36]. It is reported that silver nanowires are able to provide ECAs with similar conductivity to traditional Ag flakes at much lower filler loading, meaning they can more easily form a continuous network. In this paper, we developed a room temperature treatable, high-efficient and seedless TSV process for MEMS packaging by using a kind of novel ECAs filled with 30 wt% silver nanowires. The resistivity of a fully filled TSV was as low as 10−3 Ω·cm by orders of magnitude, which was applicable for MEMS packaging electrically. Additionally, the TSV process carried out at room temperature with a one-step filling process in a short time also shows universal in via metallization and great potential in flexible microsystems.

2. Materials and Methods

2.1. Chemicals and Materials

Silver nitrate (AgNO3, 99%), sodium chloride (NaCl, 99%), poly (vinylpyrrolidone) (PVP, K30, Mw ≈ 40,000), propanetriol (C3H8O3, 99%) were purchased from Sinopharm Chemical Reagent Co., Ltd. (Shanghai, China). Ethanol (C2H5OH, 99.9%), acetone (C3H6O, 99.9%), ammonium hydroxide (NH4OH, 99.9%), hydrogen peroxide (H2O2, 99.9%), hydrofluoric acid (HF, 99.9%) and ammonium fluoride (NH4F, 99.9%) were purchased from Chengdu Cologne Chemical Co., Ltd. (Chengdu, China). Polymethyl methacrylate (PMMA, average Mw: 950,000; Tg: 105 °C) were purchased from ALLRESIST (Strausberg, Germany). All chemical reagents were used as received without further purification. Ultrapure water (18.2 MΩ·cm) was used as the solvent and cooling water.

2.2. Synthesis of Silver Nanowires

The silver nanowires were synthesized through a modified polyol process reported previously [37]. Specifically, 120.0 mL of propanetriol, 150.0 mL of a propanetriol solution containing PVP (60 mg/mL), 15.0 mL of a propanetriol solution containing NaCl (100 mM) and 14.1 mL of a propanetriol solution containing AgNO3 (1 M) were added in a 1000-mL three-necked flask at room temperature. After the flask had been capped with glass stoppers, the solution was magnetically stirred at room temperature for about 5 min. Subsequently, the capped flask was transferred into a heating jacket and heated to 210 °C under magnetic stirring. Afterwards, the solution was slowly added into equivalent cooling water. The mixed solution was stilled at room temperature overnight. Silver nanowires were purified to remove excess precursors, PVP, and NaCl by conducting filtration three times in the presence of water and ethanol. The silver nanowires were finally dispersed into a mixture of ethanol and acetone for future use. The concentration of silver element measured by Inductively Coupled Plasma-Atomic Emission Spectrometry (ICP-AES, Atomscan Advantage, Thermo Jarrell Ash Co., Boston, MA, USA) was 5.1 mg/mL.

2.3. Preparation and Conductivity Measurement of Silver Nanowires ECAs

In a typical procedure, a certain amount of the purified silver nanowires was incorporated into the PMMA matrix with stirring for about 2 h to make the fillers uniformly dispersed in matrix and meanwhile decrease the amount of solvents. To determine the appropriate amount of silver nanowires, the ECAs filled silver nanowires with 20, 30, and 40 wt% loadings were prepared, respectively. Two strips of polyimide tape were applied onto a pre-cleaned glass slide with a gap width of 1 cm. The formulated ECAs was bladed into the space between the two strips. The polyimide tapes were removed before curing. The resistance of silver nanowires ECAs with different loadings was monitored every 15 min by multimeter (LINI-T UT58D, Uni-Trend Technology Co., Dongguan, China) in a 2-wire configuration until the resistance began to hardly change. The resistivity ρ of the fully cured silver nanowires ECAs was calculated by the Equation (1):

| (1) |

where Rs and ω are the sheet resistance and thickness of a sample, respectively. The sheet resistance Rs was measured by Non-Contact Resistivity Measurement System (Leihighton 1510EB, Semilab LEI, Pennsylvania, MA, USA), and the average thickness ω of a sample film was obtained with a stylus profiler (KLA-Tencor P-7, KLA-Tencor Co., Milpitas, CA, USA).

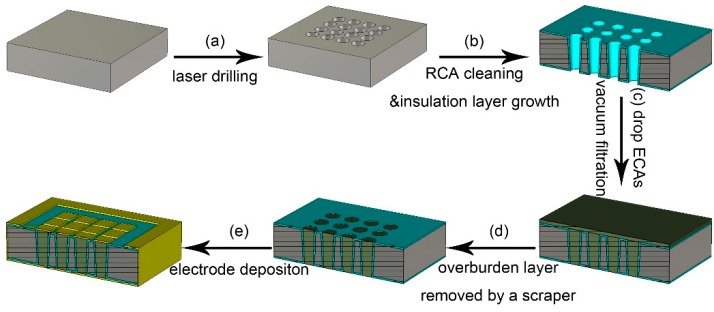

2.4. Fabrication of the Novel TSVs Process

The novel seedless TSV process based on the as-prepared room temperature curing ECAs is illustrated in Figure 1. The TSVs with an inlet diameter of 100 μm and a depth of 625 μm on a six-inch silicon wafer were attained by laser drilling (DPD02, Suzhou Delphi Laser Co., Ltd., Suzhou, China, Figure 1a). The patterned wafer was cleaned with standard RCA process (first, cleaned with 1:1:5 NH4OH:H2O2:H2O for 15 min at 75 ± 5 °C, quick dump rinse; second, cleaned with 1:10 HF:NH4F for 2 min at room temperature, quick dump rinse; finally, dried with nitrogen). Subsequently, the 320 nm SiO2 insulation layer was grown thermally by high temperature oxidation diffusion furnace (M5112-5/UM, The 48th research institute of China electronics technology group Co., Changsha, China, Figure 1b). Then the patterned wafer was diced into 2 × 2 cm2 specimens with 4 × 4 TSVs array for future use. Afterwards, a certain amount of the as-prepared sliver nanowires ECAs was dropped onto a specimen and then the sample was put into a vacuum filtration system (Figure 1c). Subsequently, the vacuum pump was turned on to perform the filling process. After the process was finished, the sample was taken out and was cured at room temperature for a certain time. After being fully cured, the overburden layer was easily removed by a scraper (Figure 1d). A small amount of residue on the surface of the filled TSV substrate was gently wiped off with clean cloth dipped in a small amount of anhydrous ethanol and then the substrate was dried with nitrogen. The surface of the substrate was characterized by a super depth of focus microscope (VHX-5000, KEYENCE, Osaka, Japan). Pad metals with 20 nm Ti/80 nm Au were finally deposited on the front and back of the substrate by sputtering. The front pads were deposited with a shadow mask that was obtained by laser drilling with 2 × 2 mm2 square patterns (Figure 1e). The resistance of filled TSVs was measured by a manual analytical probe station equipped with a four-point probe. The profiles of the filled TSVs cured at room temperature for a certain time were examined by scanning electron microscope (SEM, FEI Co., Hillsboro, OR, USA).

Figure 1.

Schematic images of the TSVs fabrication process.

2.5. Characterizations

SEM images were collected on a FEI Nova NanoSEM 650 field emission scanning electron microscope (FEI Co., Hillsboro, OR, USA) operating at 15 kV accelerating voltage. Optical images were collected on a VHX-5000 super depth of focus microscope (KEYENCE, Osaka, Japan). ICP-AES (Atomscan Advantage, Thermo Jarrell Ash, Waltham, MA, USA) was used to determine the concentration of silver. X-Ray Diffraction (XRD) characterization was performed using a X’Pert Pro X-ray diffractometer (PANalytical B.V., Almelo, The Netherlands) with a monochromatized Cu Kα radiation source and a wavelength of 0.1542 nm. The sheet resistance of silver nanowires ECAs coated on a glass slide was measured on a Leihighton 1510EB Non-Contact Resistivity Measurement System (Semilab LEI, Lehighton, PA, USA). The average thickness of a sample film was obtained with a KLA-Tencor P-7 stylus profiler (KLA-Tencor Co., Milpitas, CA, USA). A KEYSIGHT B29021 sourcemeter (KEYSIGHT TECHNOLOGIES Co., Santa Rosa, CA, USA) attached to a LAB150 manual analytical probe station (Shenzhen zhanxin technology Co., Ltd., Shenzhen, China) was used for electrical characterization of fully filled TSVs.

3. Results and Discussion

3.1. Characterization of Silver Nanowires

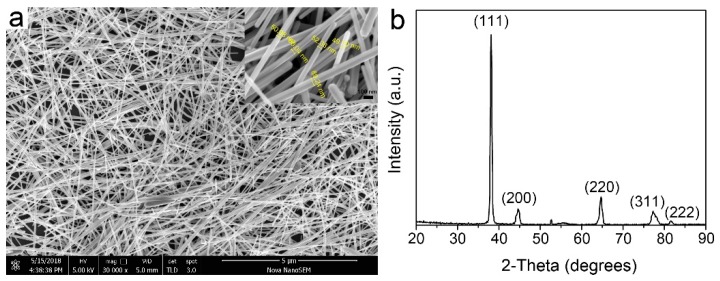

Figure 2a shows a typical SEM image of the synthesized silver nanowires. The inset is the local amplification image. The SEM images show that the as-prepared silver nanowires have a length of about 6~13 μm and diameter of 50~90 nm. Rare Ag nanoparticles were observed in Figure 2a (purity > 95%). Moreover, through purifying silver nanowires using the vacuum filtration method, the breakage of silver nanowires could be dramatically avoided. The face-centered cubic (fcc) structure of the silver nanowires was revealed by the XRD spectrum in Figure 2b. Five diffraction peaks could be observed and indexed to the (111), (200), (220), (311) and (222) planes, respectively. The lattice constant calculated from these XRD patterns was 4.0812 Å, which was close to the reported data 4.0862 Å (Joint Committee Powder Diffraction Standards, JCPDS file 04-0783).

Figure 2.

(a) SEM images of silver nanowires after being purified and (b) XRD spectrum of the synthesized silver nanowires.

3.2. Morphology and Electrical Properties Analysis on the Novel ECAs

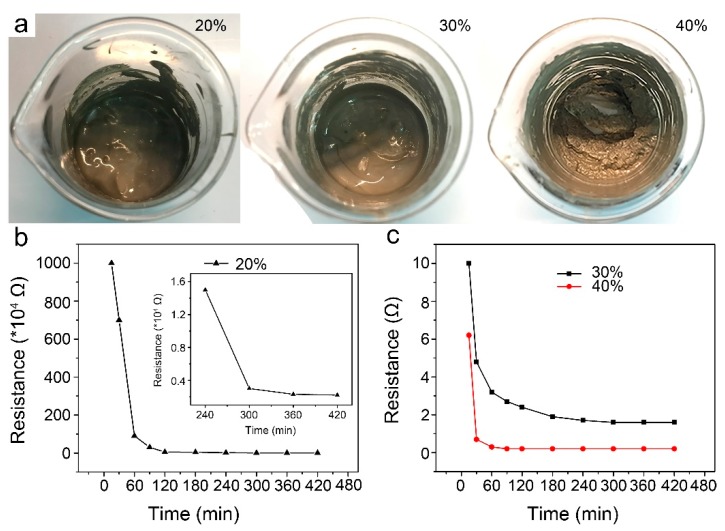

The photos of the ECAs filled silver nanowires with different loadings are represented in Figure 3a. When the loading was 20 wt%, silver nanowires could be uniformly dispersed in the PMMA matrix. As the loading of silver nanowires was increased to 30 wt%, the dispersibility of silver nanowires in the PMMA matrix was kept very well. While the loading continuing to be increased to 40 wt%, silver nanowires were difficult to be dispersed in the PMMA matrix, and the ECAs became less viscous and flowing.

Figure 3.

(a) Photos of the ECAs filled silver nanowires with 20, 30, and 40 wt% loadings. (b,c) The variations in resistance of ECAs filled silver nanowires with different loadings during curing at room temperature for 7 h: (b) 20 wt%, (c) 30 and 40 wt%. The inset in Figure 3b shows the locally magnified curve.

The resistance of ECAs is one of the most important parameters relating to interconnect reliability. Hence, in-situ monitoring of the variation in resistance of the as-prepared ECAs was undertaken at room temperature, as shown in Figure 3b,c. For ECAs filled with 20 and 30 wt% silver nanowires, the resistance was so high before curing that it was beyond the range of the multimeter. However, for the ECAs filled with 40 wt% silver nanowires, the resistance was monitored to be about 260 Ω before curing, indicating that the higher content of silver nanowires led to easier formation of the conductive networks. When curing was proceeded to 15 min, the resistance of the ECAs filled with 20 and 30 wt% silver nanowires was decreased to 10 MΩ and 10 Ω, respectively. The resistance of the ECAs filled with 20 wt% silver nanowires continued decreasing to 3 kΩ at 5 h and had little change from 5 to 7 h, signifying that the effective conductive networks had been established when curing proceeded to 5 h. According to Figure 3c, we could similarly deduce that for ECAs filled with 30 and 40 wt% silver nanowires, the effective conductive networks were established when curing proceeded to 3 and 1 h, and the corresponding resistance was 1.7 and 0.2 Ω, respectively. As such, it can be presumed that the higher silver nanowires contents are, the more conductive paths are formed in a shorter curing time, which is consistent with the literature [33,34].

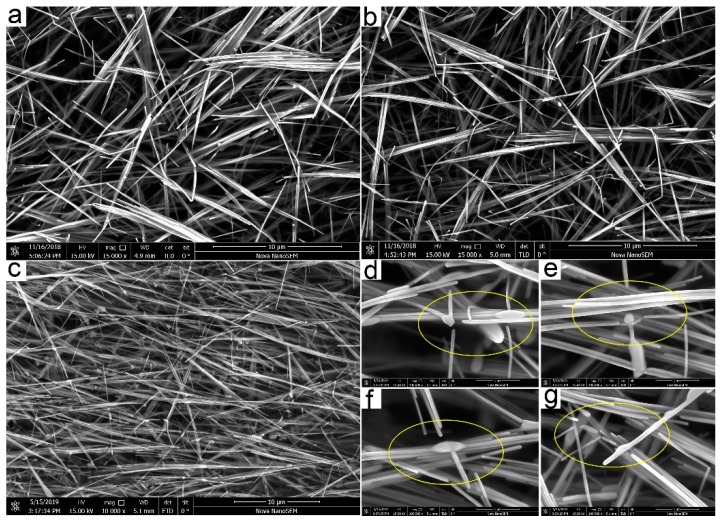

To verify whether the complete curing had been carried out at room temperature and the compatibility of the room temperature cured ECAs with a subsequent low- or high-temperature bonding process, the cured ECAs filled with 30 wt% silver nanowires continued to be cured at 180 °C and 250 °C for 20 min in a vacuum oven, respectively. The resistance was measured to be 1.1 Ω after 180 °C heat curing, showing little change. The SEM images in Figure 4a,b show the conductive networks before and after the ECAs being cured at 180 °C. There was nearly no difference in the distribution and the morphology of silver nanowires, which further demonstrated that effective conductive networks had been established at room temperature. Based on previous reports [38,39,40], we deduced that it was PMMA which contributed to the cold curing of the as-prepared ECAs and that the silver nanowires accelerated the curing process. Nevertheless, the resistance increased obviously from 1.7 to 20 Ω after 250 °C heat curing. As represented in Figure 4c–g, large amounts of sintering and fracture are observed in the silver nanowires, which leads to localized disruption of the three-dimensional conductive network and an irreversible increase in resistance of the ECAs. As such, we speculated that the room-temperature cured ECAs cannot provide a robust contact with low resistance during the high temperature bonding process (> 200 °C). However, the applications of the ECAs in TSV technology will not be limited due to the low-temperature (< 200 °C) bonding technology innovations that can overcome issues related to the high temperature bonding process, for instance, cracks of thinned and fragile wafer during bonding, performance degradation under higher bonding temperature, serious wafer/chip warpage, bonding misalignment, and compatibility with the back-end-of-line process conditions and materials [41,42,43].

Figure 4.

SEM images of the ECAs filled with 30 wt% silver nanowires before (a) and after (b) being heated at 180 °C for 20 min in a vacuum oven. (c) SEM image of the ECAs cured at 250 °C for 20min. (d–g) Localized magnified SEM images of sintering and fracture in the silver nanowires shown in (c).

After confirming that the as-prepared ECAs were fully cured at room temperature, we calculated the resistivity to evaluate the conductivity by the Equation (1) depicted in Section 2.3. The resistivity of the ECAs filled with 30 and 40 wt% silver nanowires was 4.8 × 10−3 and 6.0 × 10−4 Ω·cm, respectively, which was comparable to that of other reported high-quality ECAs [33,34]. Note that, unlike the previously reported ECAs composed of epoxy resin, curing agent, curing catalyst, etc., the ECAs prepared herein combined the benefits of both PMMA and silver nanowires. Such a combination is novel and the ECAs can be fully cured at room temperature and also exhibit excellent conductivity, showing great potential in MEMS packaging and flexible microsystems.

3.3. The Seedless TSV Process Based on the As-Prepared ECAs and Properties Analysis on the Fully Filled TSVs

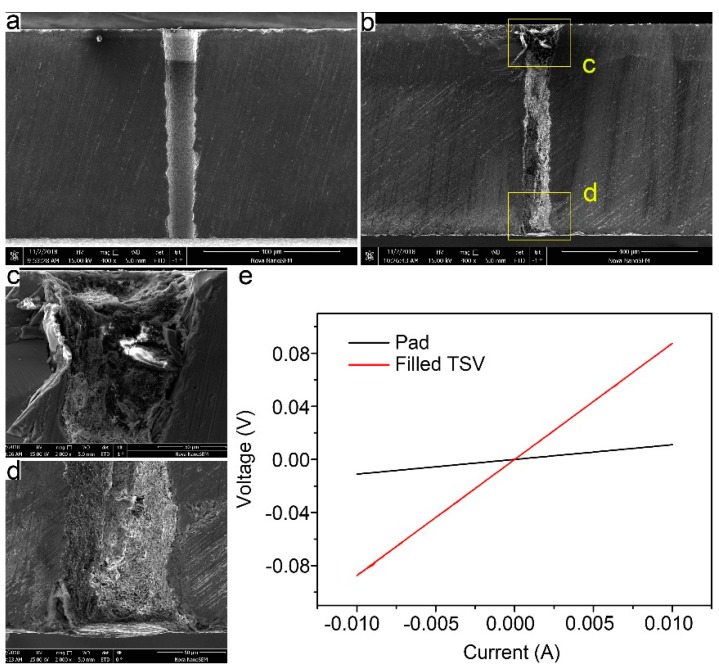

The excellent fluidity and conductivity of the as-prepared ECAs make them promising candidates for the TSV metallization process. In this work, the complete filling of TSVs with 30 wt% silver nanowires ECAs was realized through a simple one-step vacuum filtration process. Figure 5a shows the cross-sectional SEM images of the fabricated TSV with a SiO2 insulation layer, demonstrating a nearly vertical TSV with a depth of about 625 μm and an inlet diameter of about 100 μm. In contrast to TSV applications in other three-dimensional (3-D) integrations, such as memories or ICs, the feature size of TSV in MEMS packaging is relatively large, at up to hundred microns. Therefore, the size we designed here is suitable for MEMS packaging. The profile of a TSV filled with the 30 wt% silver nanowires ECAs after being cured for 3 h at room temperature was confirmed and represented in Figure 5b, indicating the TSV has been fully filled through the facile filtration process. The removal of the overburden layer was simply carried out by a scraper and clean cloth without surface contamination due to the integrality and easy cleaning of fully cured overburden ECAs layer, as shown in Figure S1. Figure 5c,d represents the corresponding magnified images of the regions marked in Figure 5b. Some cracks and voids were observed in the filled TSV, which might adversely affect the electrical conductivity of the filled TSV. Therefore, further investigations are still required to improve viscosity and liquidity of the silver nanowires ECAs, and to perfect the TSVs filling approach. In spite of this, the simple and robust filling method of TSVs with room temperature curing 30 wt% silver nanowires ECAs shows great potential in via metallization.

Figure 5.

(a,b) Cross-sectional SEM images of a TSV before (a) and after (b) being filled with 30 wt% silver nanowires ECAs. (c) and (d) show the magnified images of top and bottom of the filled TSV marked with boxes in (b), respectively. (e) I-V measurement curves of a fully filled TSV with 30 wt% silver nanowires ECAs (red) and deposited Ti/Au pad (black).

Figure 5e shows the I-V curves of a fully filled TSV (red) and deposited Ti/Au pad (black), which were obtained by a sourcemeter attached to a manual analytical probe station equipped with a four-point probe. According to the I-V curves, the resistance of a fully filled TSV was calculated to be 7.5 Ω (the resistance of Ti/Au pad had been deducted). That was about twice the theoretical value, which was calculated to be 3.7 Ω by the Equation (2):

| (2) |

where ρ is the resistivity of the ECAs filled with 30 wt% silver nanowires, L is the depth of the TSV, and S is the cross sectional area of the TSV. Nevertheless, the resistance was still applicable for MEMS packaging electrically and the TSV fabrication process shows great potential in the MEMS packaging field.

3.4. Extending the Novel Seedless TSV Process to Other Substrates

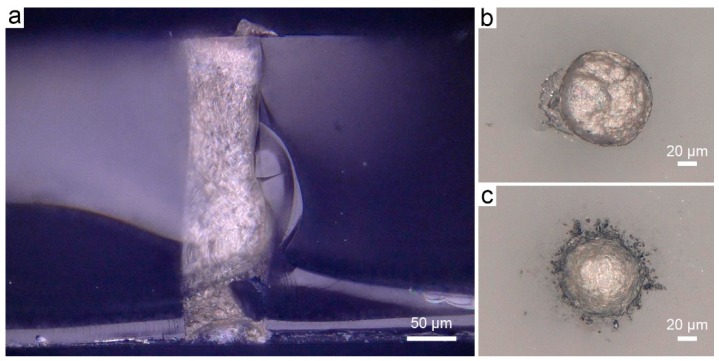

To demonstrate the universality of the room temperature treatable, low-cost, and high through-put TSV process mentioned above, this process was applied to the vias of other materials, e.g., the through glass vias (TGVs), another attractive technique in MEMS and other 3-D packaging fields [44,45]. Figure 6 represents the profile of a TGV filled with the 30 wt% silver nanowires ECAs and cured for 3 h at room temperature. The via with a depth of about 300 μm and an inlet diameter of about 100 μm was fully filled, as depicted in Figure 6a. In addition, the top and bottom of a filled-via were flat and leveled with the substrate surface, as shown in Figure 6b,c. Then the I-V curve of a fully filled TGV was obtained by using the same test method as that of TSVs, as shown in Figure S2. According to the I-V curves, the resistance of a fully filled TGV was calculated to be 4.3 Ω (the resistance of Ti/Au pad had been deducted), showing a similar resistivity to that of a fully filled TSV. As such, the simple, cost-effective, high through-put and robust filling method of through unknown vias (TXVs) with room temperature curing ECAs shows great potential and universal in via metallization for MEMS and other packaging applications.

Figure 6.

(a) The optical magnified cross-sectional image of a TGV filled with the 30 wt% silver nanowires ECAs. (b) and (c) show that the top and bottom of a fully filled TGV are flat and leveled with the substrate surface.

4. Conclusions

In summary, a typically seedless, high through-put and cost-effective TSV process based on a kind of room temperature curing ECAs for MEMS packaging and flexible microsystems was proposed in this work. The resistivity of the ECAs filled with 30 and 40 wt% silver nanowires was 4.8 × 10−3 and 6.0 × 10−4 Ω·cm after fully curing at room temperature, respectively, which was comparable to that of other reported high-quality ECAs and is also suitable for MEMS packaging electrically. By carefully controlling the pressure differential between the top and bottom ends of a TSV, the full-filling of TSVs with 30 wt% silver nanowires ECAs was realized through a one-step vacuum filtration process. In particular, this high-efficient, seedless and robust approach could serve as a general strategy for the TXVs process, showing great potential in MEMS and other 3-D packaging fields. Furthermore, the appealing room temperature curing characteristic of the strategy developed here also makes the TXVs approach for prospective candidates in flexible and other microsystems susceptible to high temperature.

Acknowledgments

The authors gratefully acknowledge Hanbin Wang, Xi Wang, and Nannan Li from CAEP for meaningful discussions. Min Meng also appreciates Rong He from Southwest University of Science and Technology (SWUST) for meaningful discussions and ICP-AES measurement.

Supplementary Materials

The following are available online at https://www.mdpi.com/2072-666X/10/6/351/s1, Figure S1. (a) Low magnification optical image of the filled TSVs array with overburden layer being removed by a scraper. (b,c) Magnified optical images of the top side of a fully filled TSV randomly selected from (a). (d,e) Magnified optical images of the back side of a fully filled TSV randomly selected from (a), Figure S2. I-V measurement curves of a fully filled TGV with 30 wt% silver nanowires ECAs (red) and deposited Ti/Au pad (black).

Author Contributions

Conceptualization, M.M.; Data curation, M.M. and L.C.; Investigation, L.C.; Methodology, M.M., K.Y., M.S. and Y.L.; Validation, Y.L.; Writing—original draft, M.M.; Writing—review & editing, Y.L.

Funding

This research received no external funding.

Conflicts of Interest

The authors declare no conflict of interest.

References

- 1.Yuan J., Jeung W.K., Lim C.H., Park S.W., Kweon Y.D., Yi S. A low-cost through via interconnection for ISM WLP. Microsyst. Technol. 2009;15:1273–1277. doi: 10.1007/s00542-008-0766-1. [DOI] [Google Scholar]

- 2.Yang H., Bakir M. 3D integration of CMOS and MEMS using mechanically flexible interconnects (MFI) and through silicon vias (TSV); Proceedings of the 60th Electronic Components and Technology Conference (ECTC); Las Vegas, NV, USA. 1–4 June 2010; pp. 822–828. [Google Scholar]

- 3.Kühne S., Hierold C. Wafer-level packaging and direct interconnection technology based on hybrid bonding and through silicon vias. J. Micromech. Microeng. 2011;21:085032:1–085032:7. doi: 10.1088/0960-1317/21/8/085032. [DOI] [Google Scholar]

- 4.Wang T., Jeppson K., Ye L., Liu J. Carbon-nanotube through-silicon via interconnects for three-dimensional integration. Small. 2011;7:2313–2317. doi: 10.1002/smll.201100615. [DOI] [PubMed] [Google Scholar]

- 5.Chen B., Sekhar V.N., Jin C., Lim Y.Y., Toh J.S., Fernando S., Sharma J. Low-loss broadband package platform with surface passivation and TSV for wafer-level packaging of RF-MEMS devices. IEEE Trans. Compon. Pack. Man. 2013;3:1443–1452. doi: 10.1109/TCPMT.2013.2263932. [DOI] [Google Scholar]

- 6.Wang Z. 3-D integration and through-silicon vias in MEMS and microsensors. J. Microelectromech. Syst. 2015;24:1211–1244. doi: 10.1109/JMEMS.2015.2448681. [DOI] [Google Scholar]

- 7.Hofmann L., Dempwolf S., Reuter D., Ecke R., Gottfried K., Schulz S.E., Knechtel R., Geßner T. 3D integration approaches for MEMS and CMOS sensors based on a Cu through-silicon-via technology and wafer level bonding; Proceedings of the SPIE 9517 on Smart Sensors, Actuators, and MEMS VII; and Cyber Physical Systems; Barcelona, Spain. 21 May 2015; pp. 951709:1–951709:12. [Google Scholar]

- 8.Menk L.A., Josell D., Moffat T.P., Baca E., Blain M.G., Smith A., Dominguez J., McClain J., Yeh P.D., Hollowell A.E. Bottom-Up Copper Filling of Large Scale Through Silicon Vias for MEMS Technology. J. Electrochem. Soc. 2019;166:D3066–D3071. doi: 10.1149/2.0091901jes. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 9.Zhang M., Yang J., He Y., Yang F., Yang F., Han G., Si C., Ning J. Research on a 3D Encapsulation Technique for Capacitive MEMS Sensors Based on Through Silicon Via. Sensors. 2019;19:93. doi: 10.3390/s19010093. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 10.Hofmann L., Ecke R., Schulz S.E., Gessner T. Investigations regarding Through Silicon Via filling for 3D integration by Periodic Pulse Reverse plating with and without additives. Microelectron. Eng. 2011;88:705–708. doi: 10.1016/j.mee.2010.06.040. [DOI] [Google Scholar]

- 11.Hong S.C., Lee W.G., Kim W.J., Kim J.H., Jung J.P. Reduction of defects in TSV filled with Cu by high-speed 3-step PPR for 3D Si chip stacking. Microelectron. Reliab. 2011;51:2228–2235. doi: 10.1016/j.microrel.2011.06.031. [DOI] [Google Scholar]

- 12.Civale Y., Armini S., Philipsen H., Redolfi A., Velenis D., Croes K., Swinnen B. Enhanced barrier seed metallization for integration of high-density high aspect-ratio copper-filled 3D through-silicon via interconnects; Proceedings of the 62ed Electronic Components and Technology Conference (ECTC); San Diego, CA, USA. 29 May–1 June 2012; pp. 822–826. [Google Scholar]

- 13.Au Y., Wang Q.M., Li H., Lehn J.M., Shenai D.V., Gordon R.G. Vapor deposition of highly conformal copper seed layers for plating through-silicon vias (TSVs) J. Electrochem. Soc. 2012;159:D382–D385. doi: 10.1149/2.097206jes. [DOI] [Google Scholar]

- 14.Shen S.P., Chen W.H., Dow W.P., Kamitamari T., Cheng E., Lin J.Y., Chang W.C. Copper seed layer repair using an electroplating process for through silicon via metallization. Microelectron. Eng. 2013;105:25–30. doi: 10.1016/j.mee.2012.12.017. [DOI] [Google Scholar]

- 15.Vartanian V.H., Allen R.A., Smith L., Hummler K., Olson S., Sapp B.C. Metrology needs for through-silicon via fabrication. J. Micro/Nanolith. MEMS MOEMS. 2014;13:011206:1–011206:9. doi: 10.1117/1.JMM.13.1.011206. [DOI] [Google Scholar]

- 16.Lau J.H., Lee C.K., Zhan C.J., Wu S.T., Chao Y.L., Dai M.J., Cheng R.S. Through-silicon hole interposers for 3-D IC integration. IEEE T. Com. Pack. Man. 2014;4:1407–1419. doi: 10.1109/TCPMT.2014.2339832. [DOI] [Google Scholar]

- 17.Gambino J.P., Adderly S.A., Knickerbocker J.U. An overview of through-silicon-via technology and manufacturing challenges. Microelectron. Eng. 2015;135:73–106. doi: 10.1016/j.mee.2014.10.019. [DOI] [Google Scholar]

- 18.Luo J., Wang G., Sun Y., Zhao X., Ding G. Fabrication and characterization of a low-cost interposer with an intact insulation layer and ultra-low TSV leakage current. J. Micromech. Microeng. 2018;28:125010:1–125010:11. doi: 10.1088/1361-6439/aae8da. [DOI] [Google Scholar]

- 19.Killge S., Bartusseck I., Junige M., Neumann V., Reif J., Wenzel C., Bartha J.W. 3D System Integration on 300 mm wafer level: High-aspect-ratio TSVs with ruthenium seed layer by thermal ALD and subsequent copper electroplating. Microelectron. Eng. 2019;205:20–25. doi: 10.1016/j.mee.2018.11.006. [DOI] [Google Scholar]

- 20.Kumar S., Greenslit D., Chakraborty T., Eisenbraun E.T. Atomic layer deposition growth of a novel mixed-phase barrier for seedless copper electroplating applications. J. Vac. Sci. Technol. A. 2009;27:572–576. doi: 10.1116/1.3122664. [DOI] [Google Scholar]

- 21.Lee J.Y., Lee S.W., Lee S.K., Park J.H. Through-glass copper via using the glass reflow and seedless electroplating processes for wafer-level RF MEMS packaging. J. Micromech. Microeng. 2013;23:085012:1–085012:10. doi: 10.1088/0960-1317/23/8/085012. [DOI] [Google Scholar]

- 22.Jee Y.K., Yu J., Park K.W., Oh T.S. Zinc and tin-zinc via-filling for the formation of through-silicon vias in a system-in-package. J. Electron. Mater. 2009;38:685–690. doi: 10.1007/s11664-008-0646-6. [DOI] [Google Scholar]

- 23.Gu J., Liu B., Yang H., Li X. A fast and CMP-free TSV process based on wafer-level liquid-metal injection for MEMS packaging; Proceedings of the 29th IEEE International Conference on Micro Electro Mechanical Systems (MEMS); Shanghai, China. 24–28 January 2016; pp. 569–572. [Google Scholar]

- 24.Ham Y.H., Kim D.P., Baek K.H., Park K.S., Kwon K.H., Do L.M. Analysis of a metal filling and liner formation mechanism of the blind via with nano-Ag particles for TSV (through silicon via) interconnection. J. Micromech. Microeng. 2012;22:075013:1–075013:8. doi: 10.1088/0960-1317/22/7/075013. [DOI] [Google Scholar]

- 25.Khorramdel B., Mäntysalo M. Fabrication and electrical characterization of partially metallized vias fabricated by inkjet. J. Micromech. Microeng. 2012;26:045017:1–045017:6. doi: 10.1088/0960-1317/26/4/045017. [DOI] [Google Scholar]

- 26.Yang T.H., Guo Z.L., Fu Y.M., Cheng Y.T., Song Y.F., Wu P.W. A low temperature inkjet printing and filling process for low resistive silver TSV fabrication in a SU-8 substrate; Proceedings of the 30th IEEE International Conference on Micro Electro Mechanical Systems (MEMS); Las Vegas, NV, USA. 22–26 January 2017; pp. 749–752. [Google Scholar]

- 27.Hai H.T., Lee K.W., Ando D., Sutou Y., Koyanagi M., Koike J. Feasibility study of Cu paste printing technique to fill deep via holes for low cost 3D TSV applications; Proceedings of the IEEE International Interconnect Technology Conference (IITC); Hsinchu, Taiwan. 16–18 May 2017; pp. 1–3. [Google Scholar]

- 28.Khorramdel B., Liljeholm J., Laurila M.M., Lammi T., Mårtensson G., Ebefors T., Mäntysalo M. Inkjet printing technology for increasing the I/O density of 3D TSV interposers. Microsyst. Nanoeng. 2017;3:17002:1–17002:9. doi: 10.1038/micronano.2017.2. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 29.Yan Y., Qian Y., Sharif H., Tipper D. A Survey on Smart Grid Communication Infrastructures: Motivations, Requirements and Challenges. IEEE Commun. Surv. Tut. 2013;15:5–20. doi: 10.1109/SURV.2012.021312.00034. [DOI] [Google Scholar]

- 30.Lai X., Liu Q., Wei X., Wang W., Zhou G., Han G. A survey of body sensor networks. Sensors. 2013;13:5406–5447. doi: 10.3390/s130505406. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 31.Liu Y., Han W., Zhang Y., Li L., Wang J., Zheng L. An Internet-of-Things solution for food safety and quality control: A pilot project in China. J. Ind. Inform. Integr. 2016;3:1–7. doi: 10.1016/j.jii.2016.06.001. [DOI] [Google Scholar]

- 32.Zhang Z.X., Chen X.Y., Xiao F. The sintering behavior of electrically conductive adhesives filled with surface modified silver nanowires. J. Adhes. Sci. Technol. 2011;25:1465–1480. doi: 10.1163/016942410X549924. [DOI] [Google Scholar]

- 33.Wang Y.H., Xiong N.N., Li Z.L., Xie H., Liu J.Z., Dong J., Li J.Z. A comprehensive study of silver nanowires filled electrically conductive adhesives. J. Mater. Sci.-Mater. El. 2015;26:7927–7935. doi: 10.1007/s10854-015-3446-9. [DOI] [Google Scholar]

- 34.Wang Y.H., Huang A., Xie H., Liu J.Z., Zhao Y.Z., Li J.Z. Isotropical conductive adhesives with very-long silver nanowires as conductive fillers. J. Mater. Sci.-Mater. El. 2017;28:10–17. doi: 10.1007/s10854-016-5487-0. [DOI] [Google Scholar]

- 35.Xiong J., Li S., Ye Y., Wang J., Qian K., Cui P., Lee P.S. A deformable and highly robust ethyl cellulose transparent conductor with a scalable silver nanowires bundle micromesh. Adv. Mater. 2018;30:1802803:1–1802803:9. doi: 10.1002/adma.201802803. [DOI] [PubMed] [Google Scholar]

- 36.Xu T., Chen J., Yuan W., Liu Y., Sun Y., Wu H., Zhou X. Self-Assembly Synthesis of Silver Nanowires/Graphene Nanocomposite and Its Effects on the Performance of Electrically Conductive Adhesive. Materials. 2018;11:2028. doi: 10.3390/ma11102028. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 37.Yang C., Gu H., Lin W., Yuen M.M., Wong C.P., Xiong M., Gao B. Silver nanowires: from scalable synthesis to recyclable foldable electronics. Adv. Mater. 2011;23:3052–3056. doi: 10.1002/adma.201100530. [DOI] [PubMed] [Google Scholar]

- 38.Beck S., Boger A. Evaluation of the particle release of porous PMMA cements during curing. Acta Biomater. 2009;5:2503–2507. doi: 10.1016/j.actbio.2009.04.002. [DOI] [PubMed] [Google Scholar]

- 39.Tillet G., Boutevin B., Ameduri B. Chemical reactions of polymer crosslinking and post-crosslinking at room and medium temperature. Prog. Polym. Sci. 2011;36:191–217. doi: 10.1016/j.progpolymsci.2010.08.003. [DOI] [Google Scholar]

- 40.Yuhana N.Y., Ahmad S., Kamal M.R., Jana S.C., Bahri A.R. Morphological study on room-temperature-cured PMMA-grafted natural rubber-toughened epoxy/layered silicate nanocomposite. J. Nanomater. 2012;2012:760401:1–760401:14. doi: 10.1155/2012/760401. [DOI] [Google Scholar]

- 41.Eaton W.P., Risbud S.H., Smith R.L. Silicon wafer-to-wafer bonding at T < 200 °C with polymethylmethacrylate. Appl. Phys. Lett. 1994;65:439–441. [Google Scholar]

- 42.Ko C.T., Chen K.N. Low temperature bonding technology for 3D integration. Microelectron. Reliab. 2012;52:302–311. doi: 10.1016/j.microrel.2011.03.038. [DOI] [Google Scholar]

- 43.Ahmad M., Bozkurt A., Farhanieh O. PMMA-Based Wafer-Bonded Capacitive Micromachined Ultrasonic Transducer for Underwater Applications. Micromachines. 2019;10:319. doi: 10.3390/mi10050319. [DOI] [PMC free article] [PubMed] [Google Scholar]

- 44.Liljeholm J., Shah U., Campion J., Oberhammer J. Through-Glass-Via Enabling Low Loss High-Linearity RF Components; Proceedings of the 11th Micronano System Workshop 2016 (MSW 2016); Tomsk, Russia. 10–15 May 2016. [Google Scholar]

- 45.Yang F., Han G., Yang J., Zhang M., Ning J., Yang F., Si C. Research on Wafer-Level MEMS Packaging with Through-Glass Vias. Micromachines. 2019;10:15. doi: 10.3390/mi10010015. [DOI] [PMC free article] [PubMed] [Google Scholar]

Associated Data

This section collects any data citations, data availability statements, or supplementary materials included in this article.