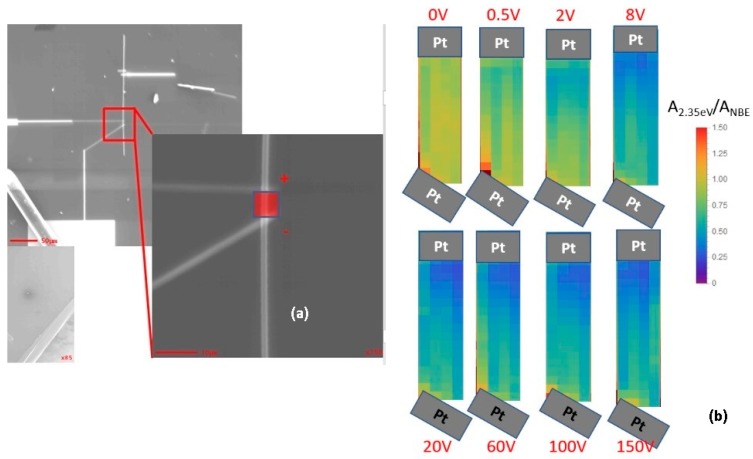

Figure 12.

(a) Pt wire layout to apply voltage across two Pt contacts spaced 5 μm apart on a 3 μm diameter ZnO nanowire. (b) HSI maps of normalized defect intensity between Pt electrodes showing segregation of defects toward bottom electrode increasing with increasing applied voltage [60].