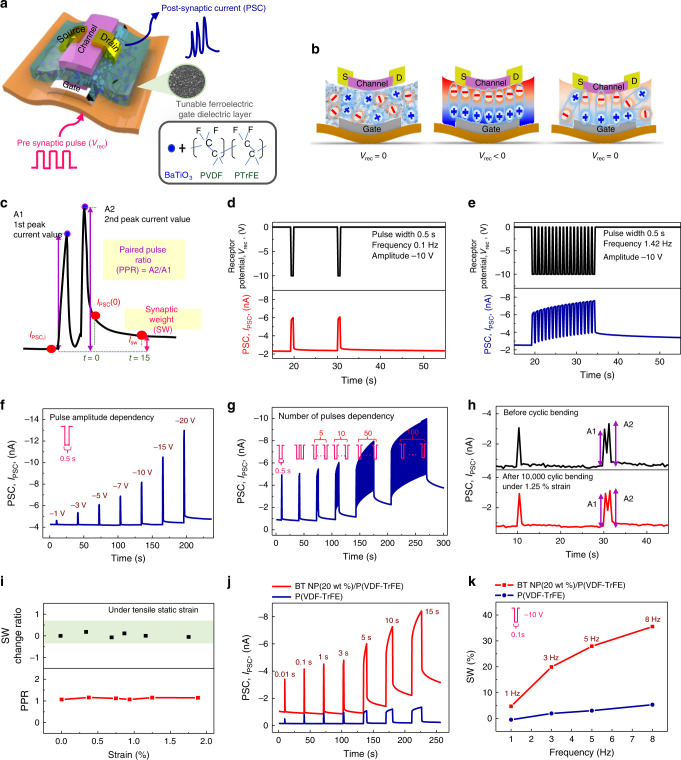

Fig. 2. Analysis of synaptic properties of Fe-OFET.

a Sketch of device structure. Pre-synaptic pulse corresponds to an electrical gate bias voltage, Vrec. Gate dielectric layer consists of BT NPs/P(VDF-TrFE) ferroelectric material. b Mechanism by which the post-synaptic current (PSC) is generated. Schematic explaining the alignment of ferroelectric dipoles before applying Vrec (left), during application of a negative Vrec (middle), and after removal of the Vrec (right). c Schematic explanation of synaptic weight (SW) and paired pulse ratio (PPR). d, e Short-term potentiation (frequency of 0.1 Hz, d) and long-term potentiation (frequency of 1.42 Hz, e) were triggered by applying −10 V Vrec pulses. PSC dependence on f Vrec amplitude (pulse width, 500 ms). g Number of Vrec pulses (amplitude of −10 V and pulse width of 500 ms). h PSC before (black) and after (red) a cyclic bending test. PSC in response to a pulse and successive pulses of −10 V Vrec with a pulse width of 500 ms (pulse interval of successive identical pulses, Δtrec = 500 ms). i Variations in SW change ratio and PPR under different static tensile strain. PSC of devices with BT NP(20 wt%)/P(VDF-TrFE) (red) and P(VDF-TrFE) only (blue) (j), as a function of Vrec pulse duration. (amplitude of Vrec, −10 V) (k), at different frequencies of Vrec (amplitude of −10 V).